# OPTIMIZED SPARSE MATRIX OPERATIONS AND HARDWARE IMPLEMENTATION USING FPGA

by

Dinesh Kumar Murthy, B.E.

A thesis submitted to the Graduate Council of Texas State University in partial fulfillment of the requirements for the degree of Master of Science with a Major in Engineering August 2021

Committee Members:

Semih Aslan, Chair

Dan Tamir

Bill Stapleton

Jesus Jimenez

# **COPYRIGHT**

by

Dinesh Kumar Murthy

2021

## FAIR USE AND AUTHOR'S PERMISSION STATEMENT

#### Fair Use

This work is protected by the Copyright Laws of the United States (Public Law 94-553, section 107). Consistent with fair use as defined in the Copyright Laws, brief quotations from this material are allowed with proper acknowledgment. Use of this material for financial gain without the author's express written permission is not allowed.

# **Duplication Permission**

As the copyright holder of this work, I, Dinesh Kumar Murthy, authorize duplication of this work, in whole or in part, for educational or scholarly purposes only.

# **DEDICATION**

I would like to dedicate this thesis to my loving dad and mom for all the guidance, encouragement, and support throughout my life. I also dedicate this thesis to my friends for their constant help and support in every step of my life.

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to all who helped me during the writing of this thesis at Texas State.

First, I would like to express my deep gratitude to Dr. Semih Aslan, my supervisor, for his continuous support and encouragement, for his patience, motivation, enthusiasm, and immense knowledge. He also provides me with an excellent atmosphere for conducting this research project. Without his consistent and illuminating instruction, this thesis could not have reached its present form.

I would also like to express my heartfelt gratitude to my thesis committee members: Dr. Dan Tamir, Dr. Bill Stapleton and Dr. Jesus Jimenez for their insightful comments and constructive comments in the early and final version of the work.

I owe a special debt of gratitude to Dr. Vishu Viswanathan, Graduate Advisor of Engineering, and Dr. Stan McClellan, Former Director of Ingram School of Engineering, for providing facility support. I would like to thank Ms. Sarah Rivas in Ingram School of Engineering and Department Engineering Technology for their kind help.

Finally, I express my gratitude to my parents, family, and friends for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them.

# TABLE OF CONTENTS

|                                            | Page |

|--------------------------------------------|------|

| ACKNOWLEDGEMENTS                           | V    |

| LIST OF TABLES                             | viii |

| LIST OF FIGURES                            | ix   |

| LIST OF ABBREVIATIONS                      | xiv  |

| ABSTRACT                                   | xvi  |

| CHAPTER                                    |      |

| 1. INTRODUCTION                            | 1    |

| 1.1 Problem Statement                      | 4    |

| 1.2 Research Goals                         | 4    |

| 1.3 Goal Measurement Metrics               |      |

| 1.4 Tools Used                             | 7    |

| 2. LITERATURE REVIEW                       | 8    |

| 3. BACKGROUND                              | 12   |

| 3.1 Graph Processing                       | 12   |

| 3.2 Sparse Matrices                        |      |

| 3.3 Sparse Matrix Storage Formats          |      |

| 3.4 Finite State Machines (FSMs)           |      |

| 3.5 Field Programmable Gate Arrays (FPGAs) |      |

| 3.5.1 FPGA Architecture                    |      |

| 3.5.2 Design and Programming               | 22   |

| 3.5.2.1 Design Entry                       |      |

| 3.5.2.3 RTL Analysis                       |      |

| 3.5.2.4 Synthesis                          |      |

| 3.5.2.5 Implementation                     |      |

| 3.5.2.6 Timing Analysis                    |      |

| 3.5.2.7 Power Usage Analysis               |      |

| 3.5.2.8 Programming the Board                                      | 29  |

|--------------------------------------------------------------------|-----|

| 3.5.3 NEXYS4 DDR ARTIX-7 FPGA Board                                |     |

| 4. HARDWARE DESIGN ARCHITECTURE                                    | 31  |

| 4.1 Arithmetic Operations                                          | 38  |

| 4.1.1 Sparse Matrix Addition                                       | 38  |

| 4.1.2 Sparse Matrix Multiplication                                 |     |

| 4.2 Matrix Decomposition                                           | 58  |

| 4.2.1 LU Decomposition                                             |     |

| 4.2.1.1 Sparse LU Decomposition Architecture                       | 62  |

| 4.2.1.2 Implementation and Error Analysis                          | 67  |

| 4.2.2 QR Decomposition                                             |     |

| 4.2.2.1 Householder Transformation                                 | 73  |

| 4.2.2.2 Design Flow and Optimization                               | 76  |

| 5. ALGORITHM PERFORMANCE RESULTS                                   | 85  |

| 5.1 Sparse Matrix Addition vs. Regular Matrix Addition             | 85  |

| 5.2 Sparse Matrix Subtraction vs. Regular Matrix Subtraction       | 98  |

| 5.3 Element-By-Element Multiplication                              | 101 |

| 5.4 Sparse Matrix Multiplication vs. Regular Matrix Multiplication | 104 |

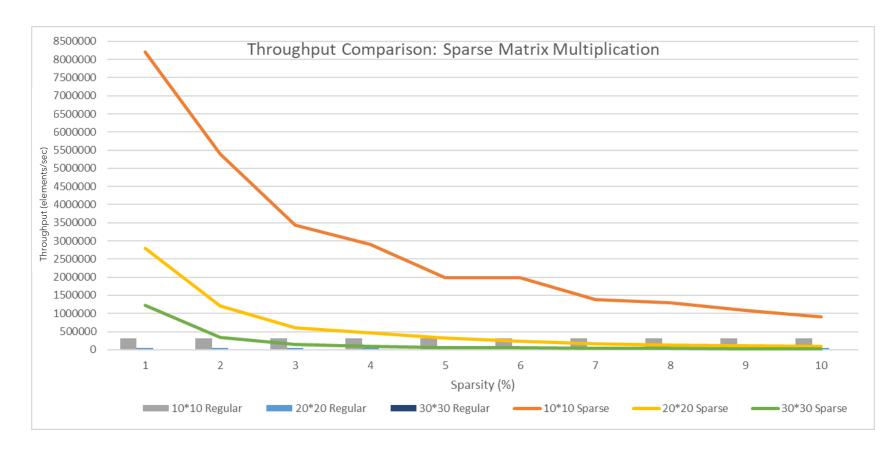

| 5.5 Sparse LU Decomposition vs. Regular LU Decomposition           | 110 |

| 5.6 Sparse QR Decomposition vs. Regular QR Decomposition           | 114 |

| 5.7 Execution Time Analysis                                        | 117 |

| 6. CONCLUSION AND FUTURE WORK                                      | 119 |

| APPENDIX SECTION                                                   | 121 |

| REFERENCES                                                         | 146 |

# LIST OF TABLES

| Table                                                                        | Page |

|------------------------------------------------------------------------------|------|

| 1. Adjacency Matrix Representation of the Graph                              | 13   |

| 2. Comparison of Various Sparse Matrix Storage Formats                       | 17   |

| 3. Computational Complexity                                                  | 32   |

| 4. Error Analysis for LU Decomposition Operation                             | 70   |

| 5. Error Analysis for QR Decomposition Operation                             | 84   |

| 6. Hardware Implementation: Sparse Matrix Arithmetic Operation               | 97   |

| 7. Latency and Throughput Comparison from Implemented Design                 | 98   |

| 8. Resources Utilization for Sparse Matrix Element by Element Multiplication | 104  |

| 9. Hardware Implementation: Sparse Matrix Multiplication                     | 108  |

| 10. Hardware Implementation: LU Decomposition                                | 113  |

| 11. Hardware Implementation: QR Decomposition                                | 115  |

| 12. Benchmark matrices, performance, and pattern                             | 117  |

# LIST OF FIGURES

| Figure                                                          | Page |

|-----------------------------------------------------------------|------|

| 1. Real World Sparse Matrix Applications                        | 1    |

| 2. Graph Representing Several Cities in Southern California     | 12   |

| 3. Sparsity Pattern of Matrices                                 | 15   |

| 4. Storage of Input Matrix                                      | 19   |

| 5. State Diagram of a Simplified Finite State Machine           | 20   |

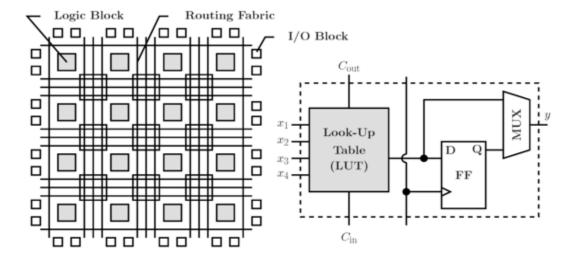

| 6. Sketch of FPGA Architecture and Design of Simple Logic Block | 22   |

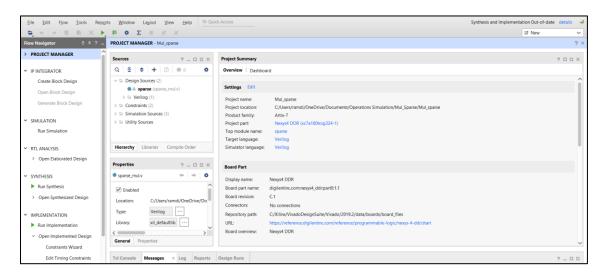

| 7. Vivado Design Suite                                          | 22   |

| 8. Vivado Project Manager                                       | 23   |

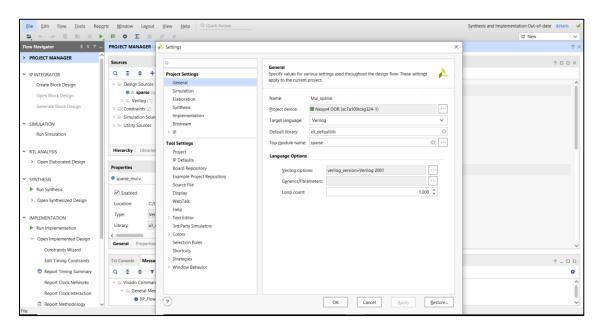

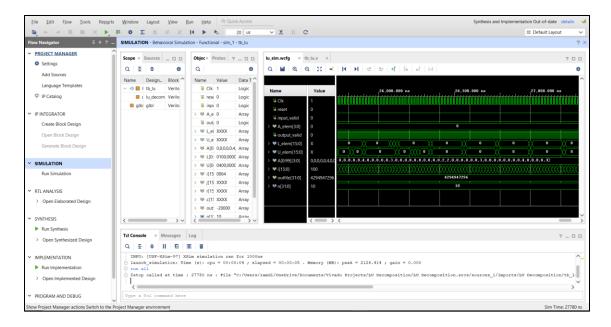

| 9. Vivado Simulation Environment                                | 24   |

| 10. Vivado RTL Analysis Tool                                    | 24   |

| 11. Vivado Synthesis Analysis Tool                              | 25   |

| 12. Vivado Synthesis Report Analysis                            | 25   |

| 13. Vivado Implementation Tool                                  | 26   |

| 14. Vivado Timing Constraints Tool                              | 27   |

| 15. Vivado Power Analysis Tool                                  | 28   |

| 16. Nexys4 DDR Artix-7 FPGA Board                               | 30   |

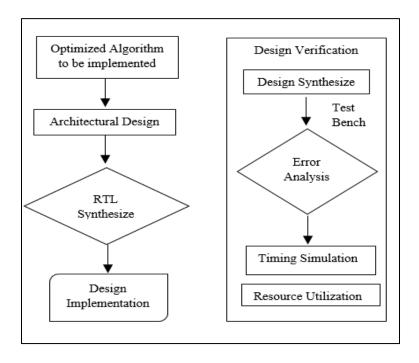

| 17. High Level Flow Chart of Work Proposed                      | 31   |

| 18. FPGA Implementation and Verification Flow                   | 32   |

| 19. Overview of Hardware and Software Implementation            | 33   |

| 20. Block Diagram of TX and RX Module                                                                            | 34 |

|------------------------------------------------------------------------------------------------------------------|----|

| 21. Clock Cycle for TX and RX                                                                                    | 35 |

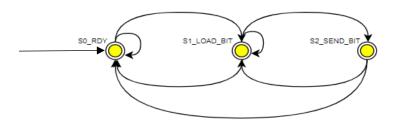

| 22. Fundamental Design: Transmission FSM                                                                         | 36 |

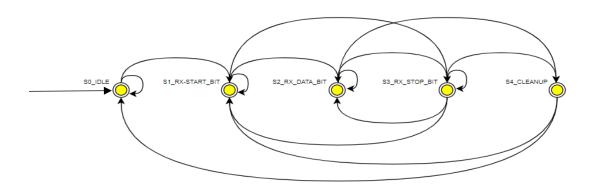

| 23. Fundamental Design: Receiver FSM                                                                             | 37 |

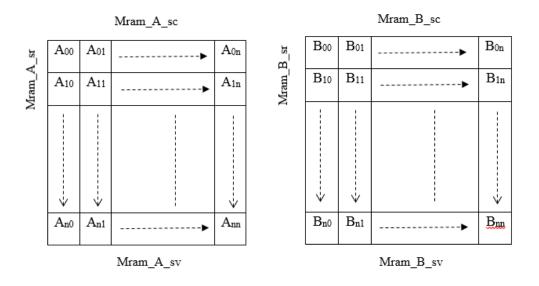

| 24. Representation of Row and Column Access of Input Matrices                                                    | 40 |

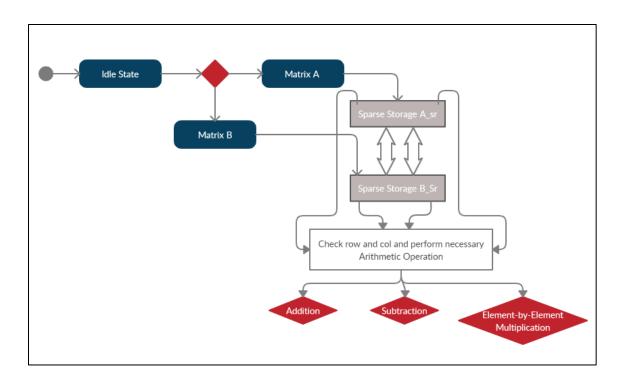

| 25. FSM Transition States for Sparse Matrix Arithmetic Operations                                                | 42 |

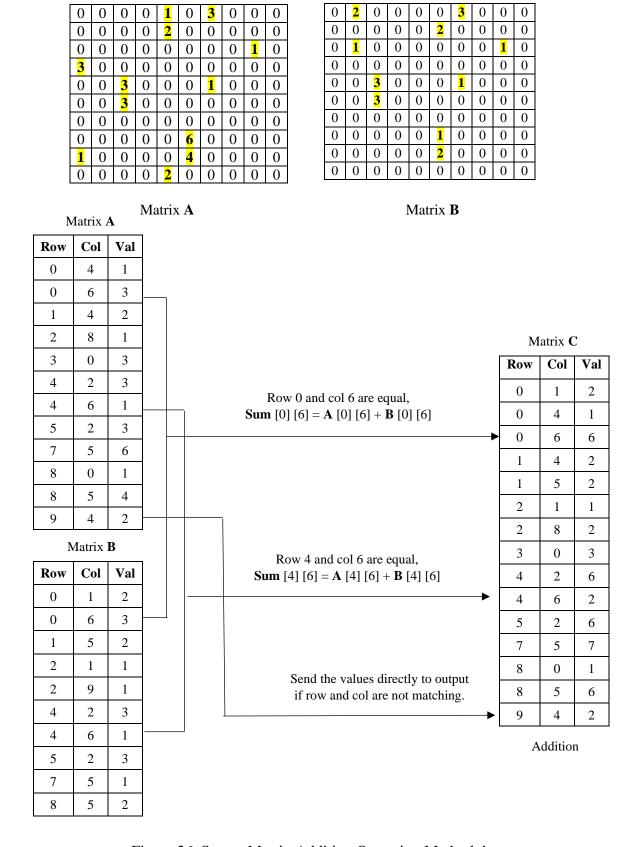

| 26. Sparse Matrix Addition Operation Methodology                                                                 | 43 |

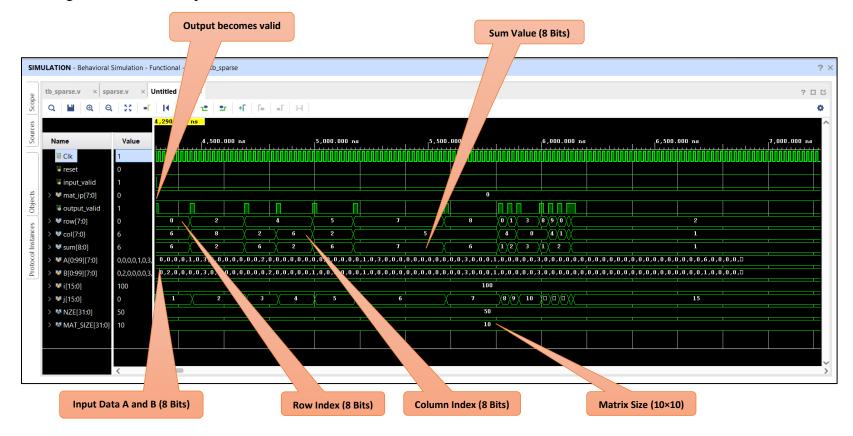

| 27. Design Simulation: Sparse Matrix Addition Operation                                                          | 44 |

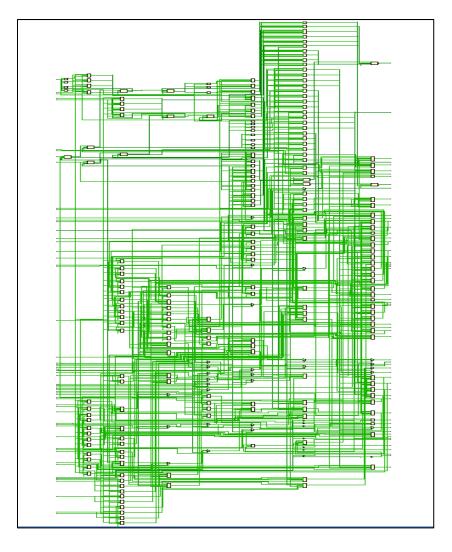

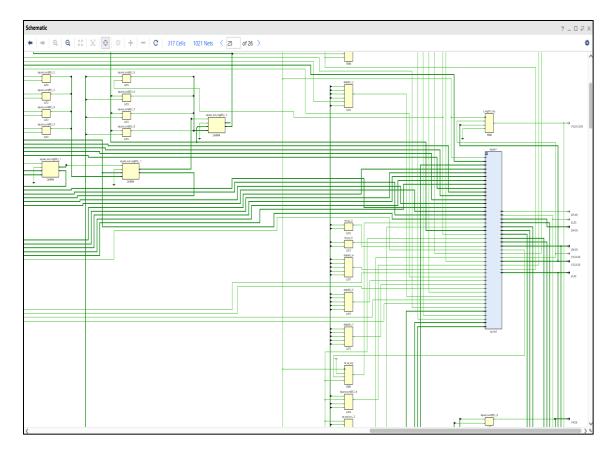

| 28. Implemented Design: Arithmetic Operation Engine                                                              | 46 |

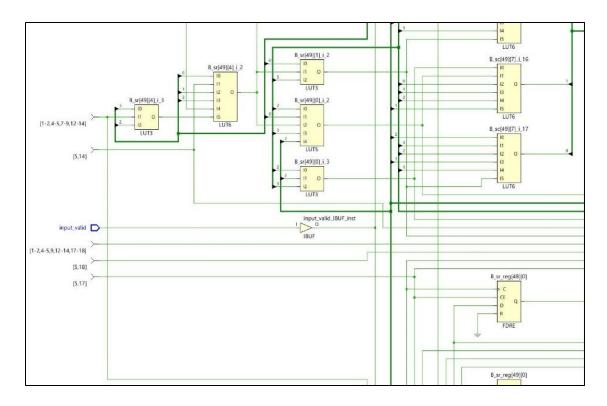

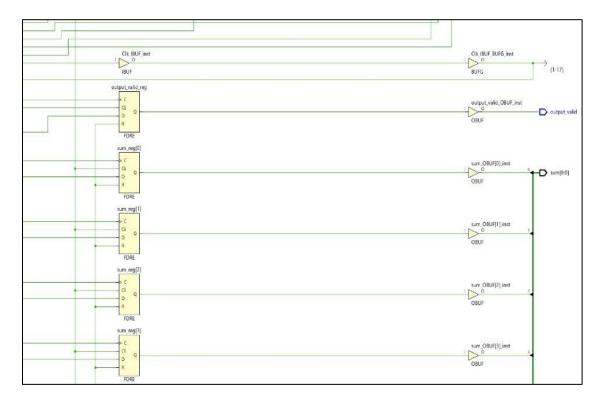

| 29. Interconnect Design: Input Valid Schematic                                                                   | 47 |

| 30. Interconnect Design: Output Valid Schematic                                                                  | 47 |

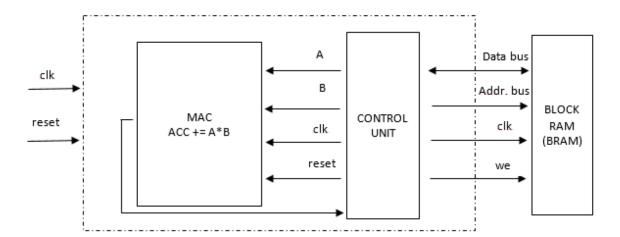

| 31. Matrix Multiplication Hardware Architecture                                                                  | 49 |

| 32. Overall Design Flow                                                                                          | 50 |

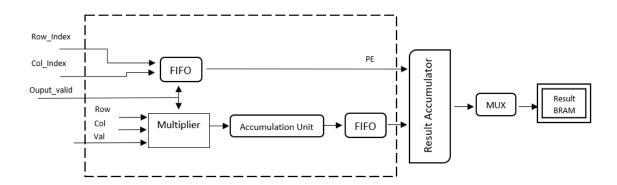

| 33. Sparse Matrix Multiplication Methodology                                                                     | 53 |

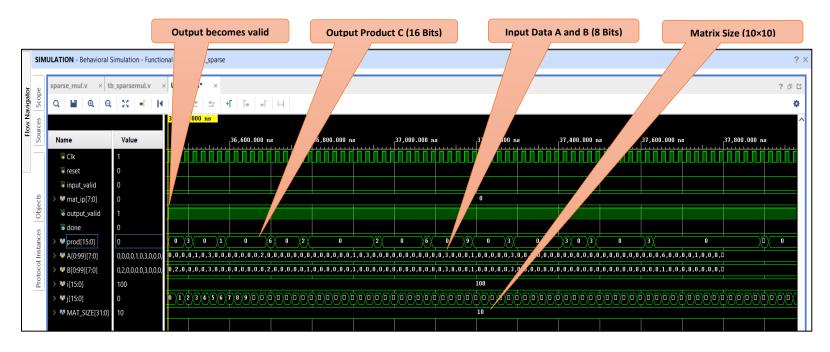

| 34. Design Simulation: Sparse Matrix Multiplication                                                              | 54 |

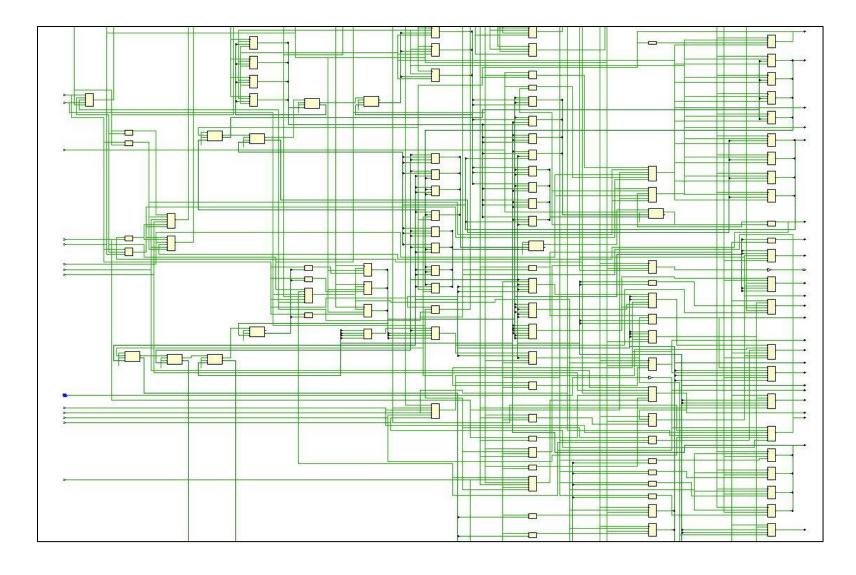

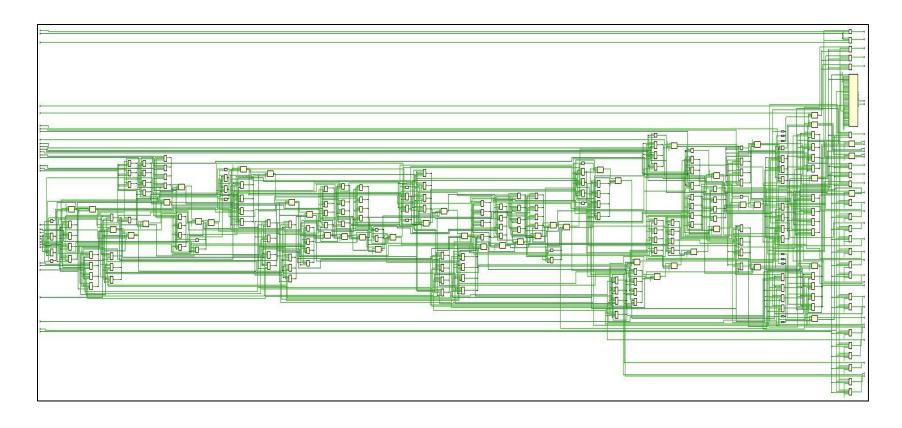

| 35. Elaborated Implemented Design: Sparse Matrix Multiplication                                                  | 55 |

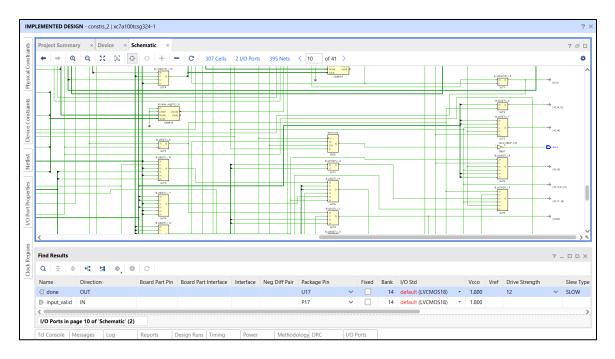

| 36. Interconnect Design: Sparse Matrix Multiplication                                                            | 56 |

| 37. Interconnect Design: Temporary Registers for Intermediate Output                                             | 57 |

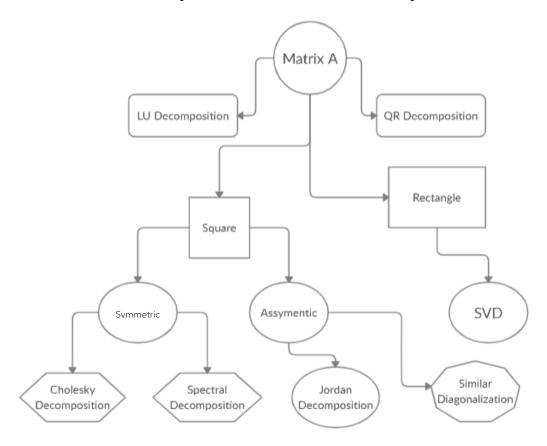

| 38. Matrix Decomposition                                                                                         | 58 |

| 39. MATLAB Representation of LU Decomposition of 20x20 Combinatorial Problem from Suite Sparse Matrix Collection | 61 |

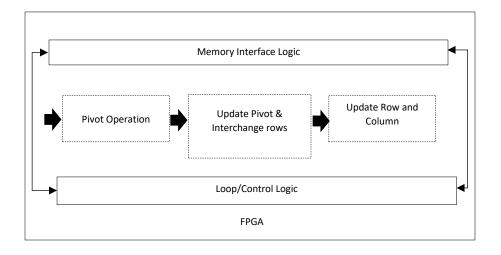

| 40. Control Logic for LU Decomposition Hardware                                                                 | 62 |

|-----------------------------------------------------------------------------------------------------------------|----|

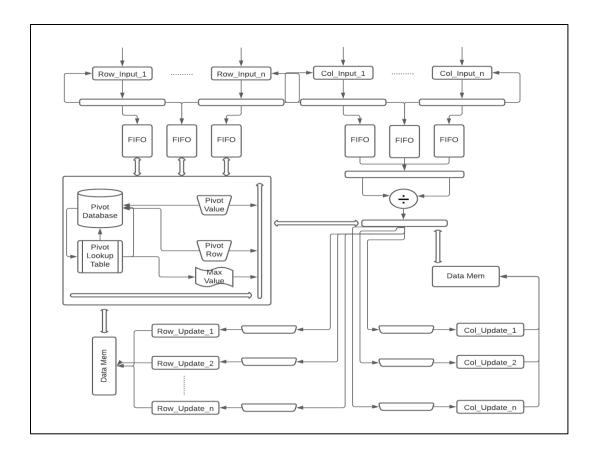

| 41. Block Diagram of Proposed LU Decomposition Hardware                                                         | 65 |

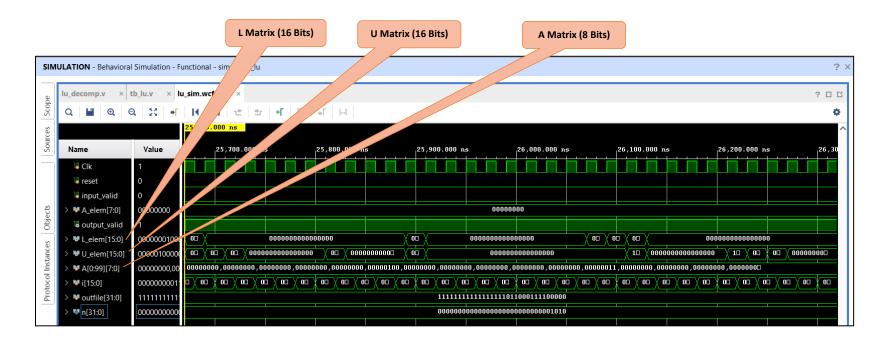

| 42. Design Simulation: LU Decomposition                                                                         | 68 |

| 43. Implemented Design Engine: LU Decomposition                                                                 | 69 |

| 44. MATLAB Representation of QR Decomposition of 100x100 Structural Problem from Suite Sparse Matrix Collection | 72 |

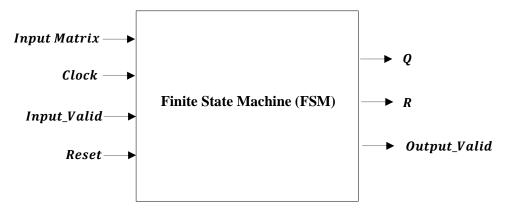

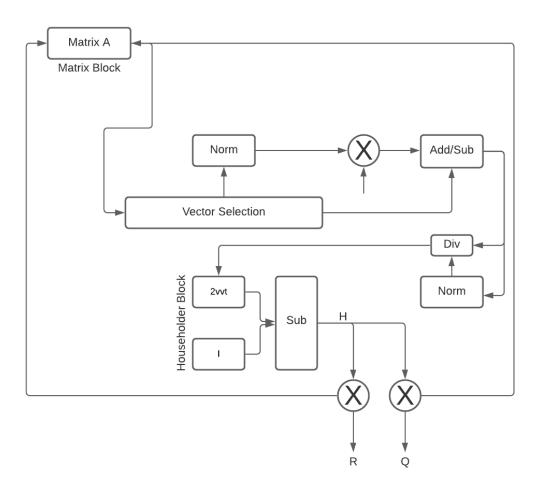

| 45. QR Decomposition Core                                                                                       | 76 |

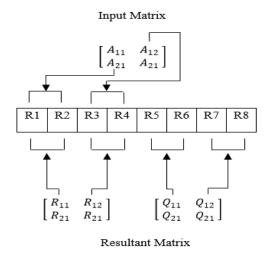

| 46. Usage of Registers for QR Decomposition of 2x2 Matrix                                                       | 77 |

| 47. Block Diagram for QR Decomposition using Householder Transformation                                         | 79 |

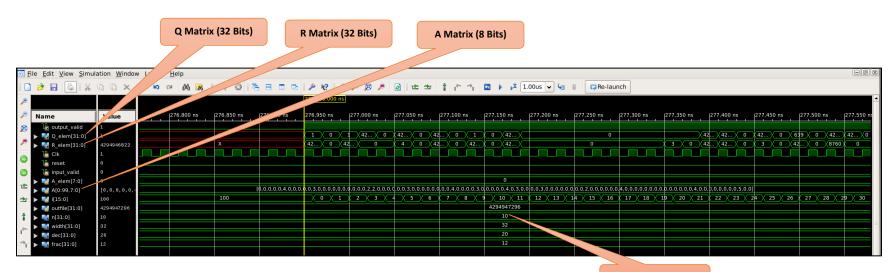

| 48.Simulation Waveform: QR Decomposition                                                                        | 80 |

| 49. Implemented Design: QR Decomposition                                                                        | 81 |

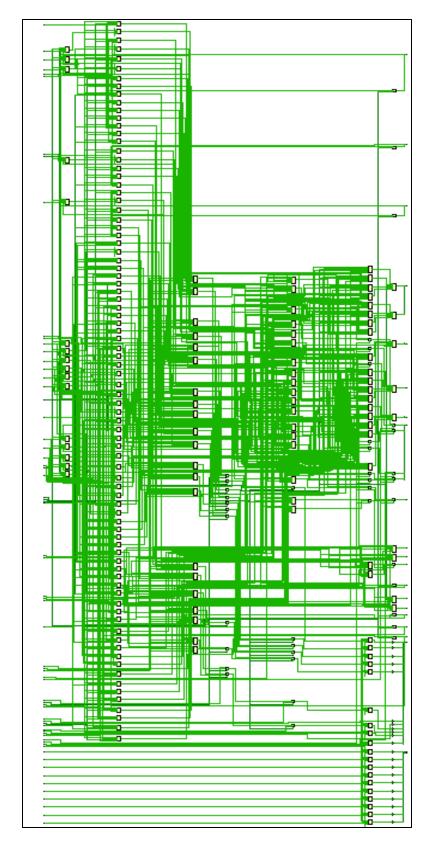

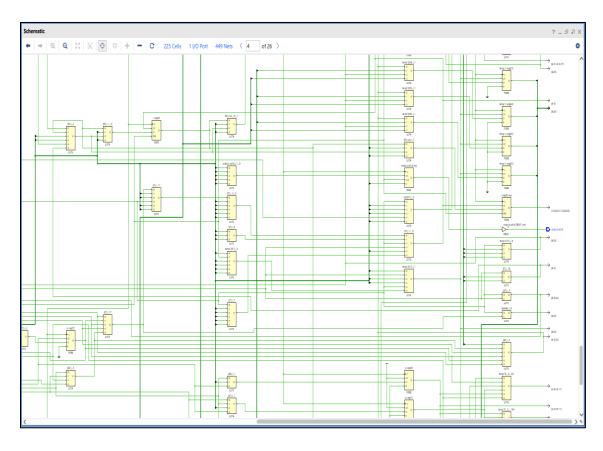

| 50. Interconnect Schematic: Output FSM                                                                          | 82 |

| 51. Interconnect Schematic: Square Root Module                                                                  | 83 |

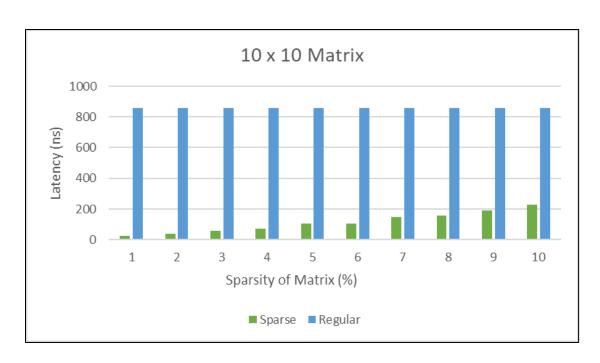

| 52. Latency Comparison: Proposed vs Regular for 10×10 Matrix                                                    | 86 |

| 53. Latency Comparison: Proposed vs Regular for 20×20 Matrix                                                    | 86 |

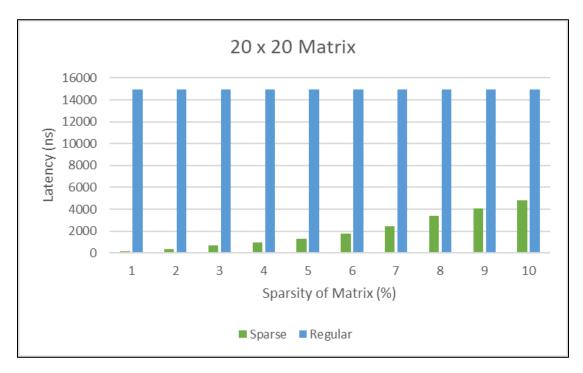

| 54. Latency Comparison: Proposed vs Regular for 30×30 Matrix                                                    | 87 |

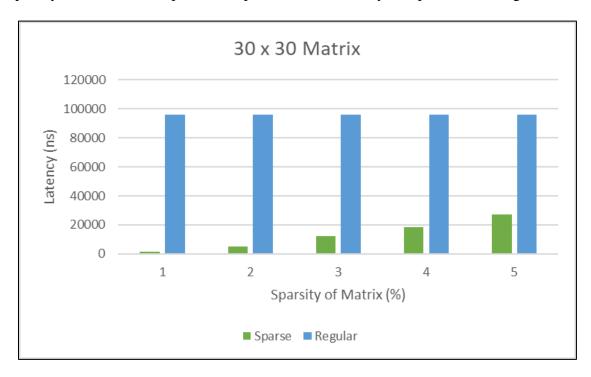

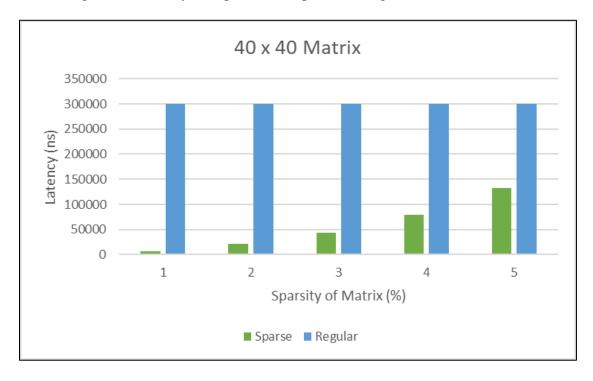

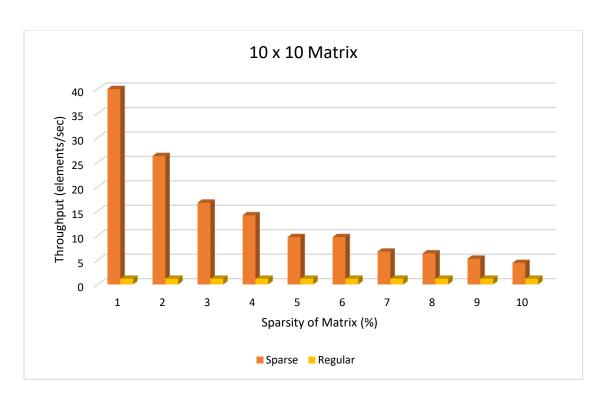

| 55. Latency Comparison: Proposed vs Regular for 40×40 Matrix                                                    | 87 |

| 56. Latency Comparison: Proposed vs Regular for 50×50 Matrix                                                    | 88 |

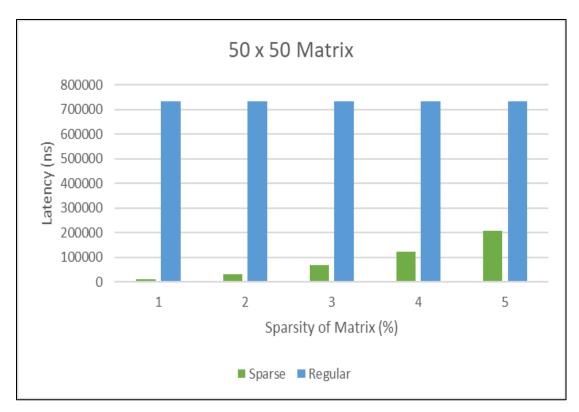

| 57. Latency Comparison: Proposed vs Regular for 100×100 Matrix                                                  | 89 |

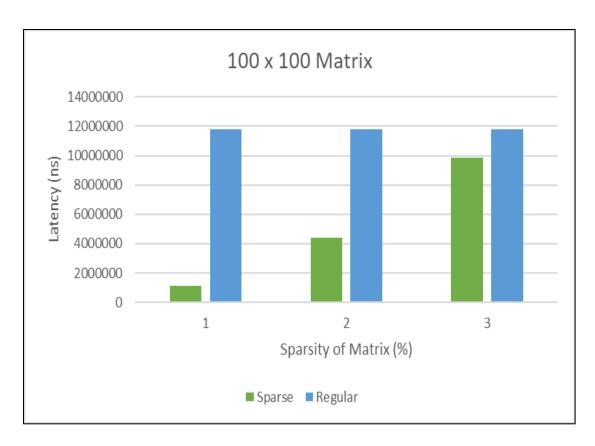

| 58. Throughput Comparison: Proposed vs Regular for 10×10 Matrix                                                 | 90 |

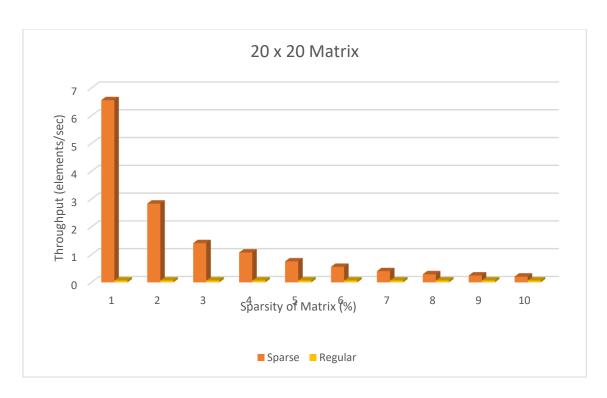

| 59. Throughput Comparison: Proposed vs Regular for 20×20 Matrix                                                 | 91 |

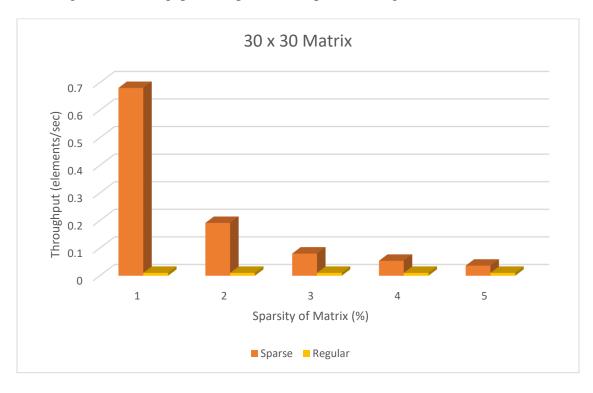

| 60. Throughput Comparison: Proposed vs Regular for 30×30 Matrix91                                         |

|-----------------------------------------------------------------------------------------------------------|

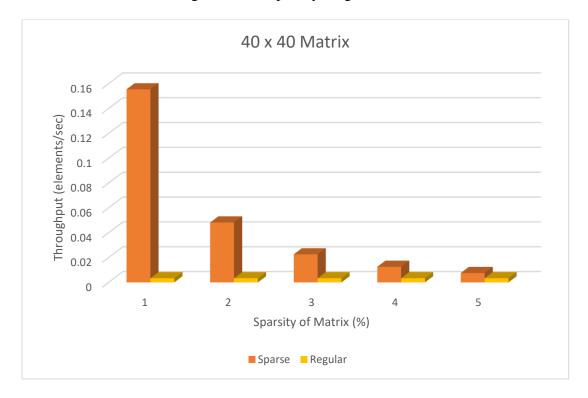

| 61. Throughput Comparison: Proposed vs Regular for 40×40 Matrix92                                         |

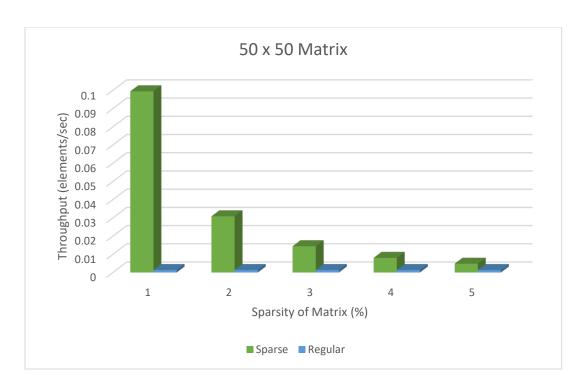

| 62. Throughput Comparison: Proposed vs Regular for 50×50 Matrix93                                         |

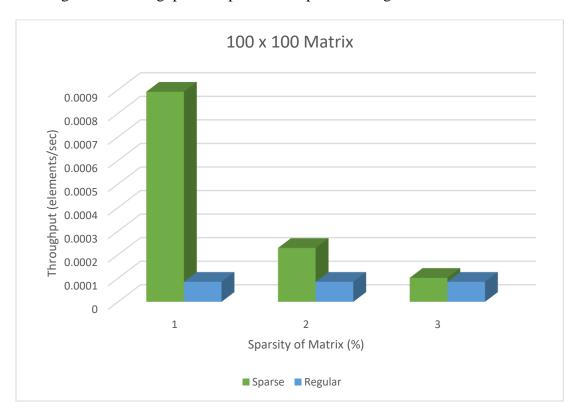

| 63. Throughput Comparison: Proposed vs Regular for 100×100 Matrix93                                       |

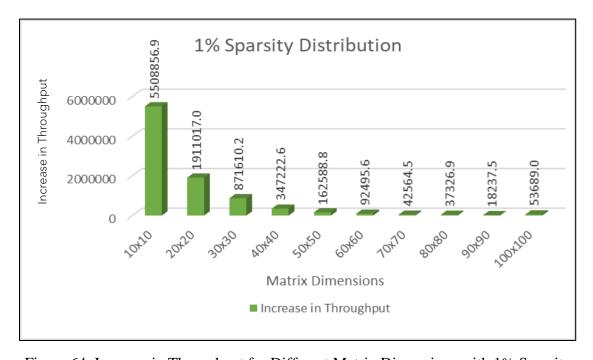

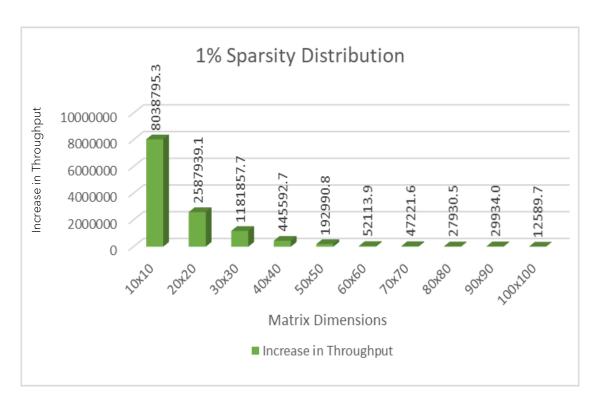

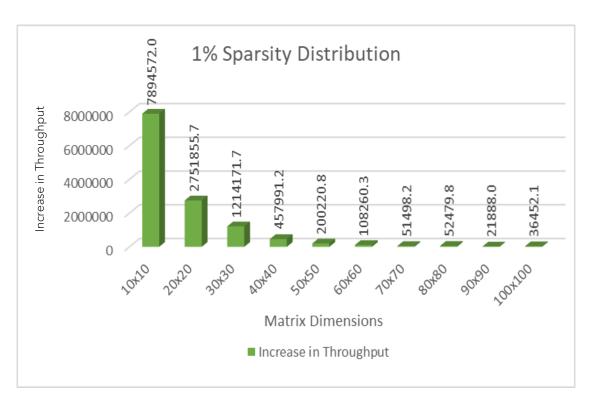

| 64. Increase in Throughput for Different Matrix Dimensions with 1% Sparsity94                             |

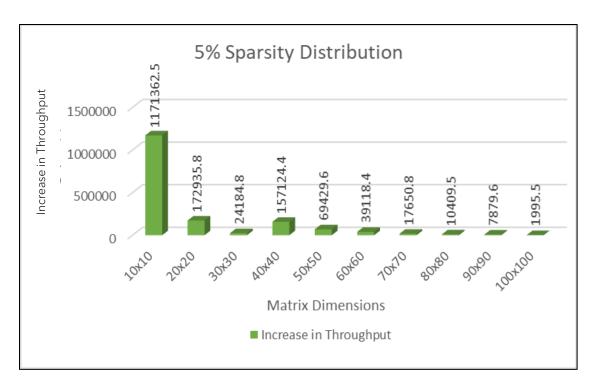

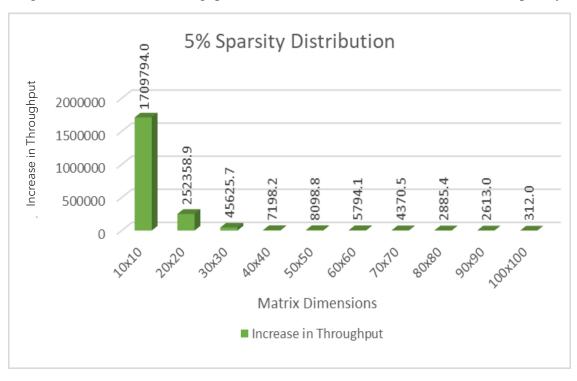

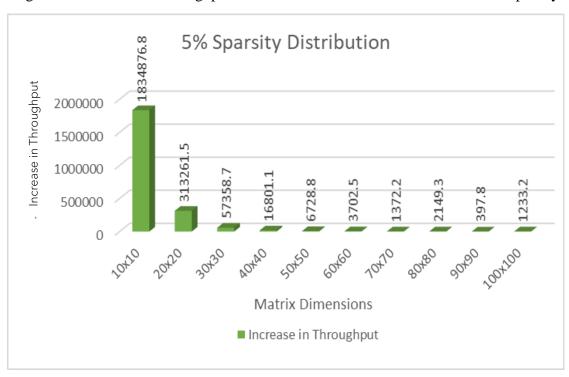

| 65. Increase in Throughput for Different Matrix Dimensions with 5% Sparsity95                             |

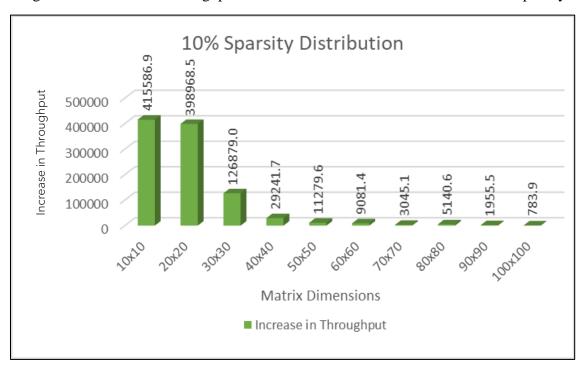

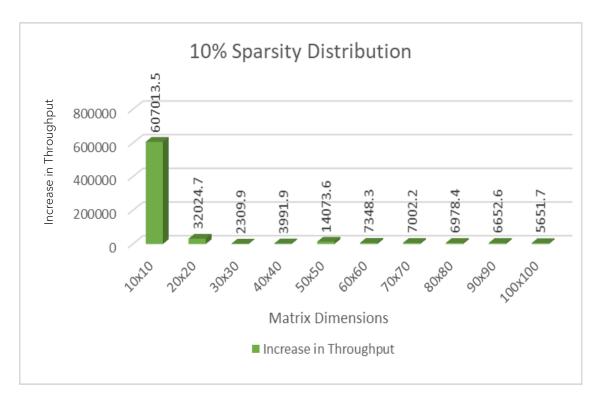

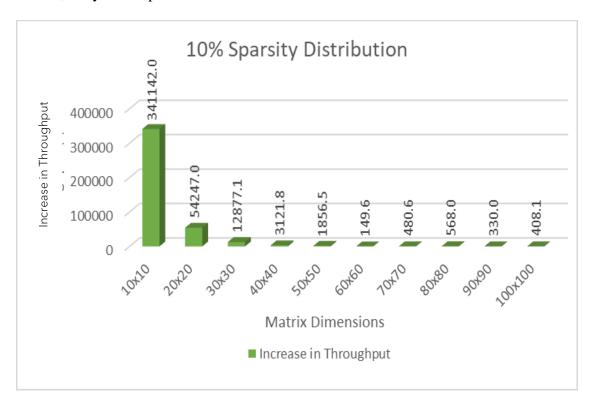

| 66. Increase in Throughput for Different Matrix Dimensions with 10% Sparsity95                            |

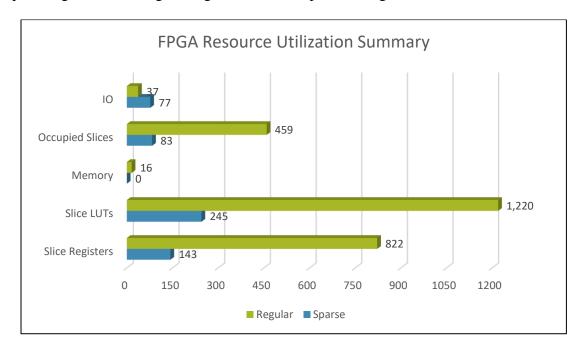

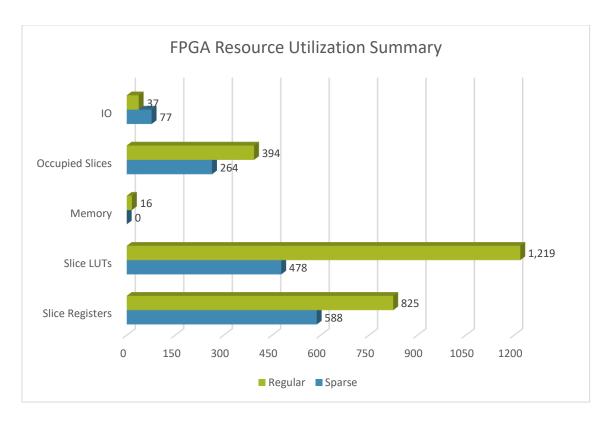

| 67. FPGA Resource Utilization: Regular vs Sparse-Sparse Matrix Addition Operation96                       |

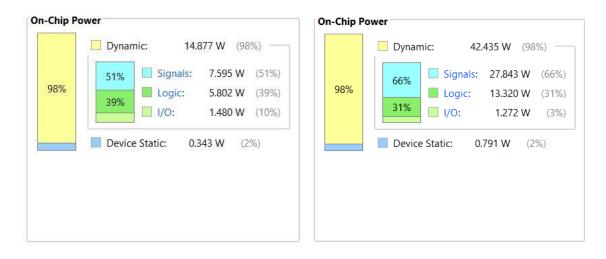

| 68. Power Analysis: Sparse Matrix Arithmetic Operation                                                    |

| 69. FPGA Resource Utilization: Regular vs Sparse-Sparse Matrix Subtraction Operation                      |

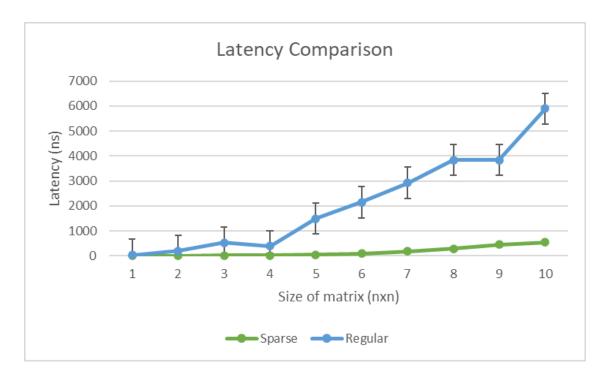

| 70. Latency Comparison: Proposed vs Regular for Sparse Matrix Element-by-Element Multiplication Operation |

| 71. Increase in Throughput for Different Matrix Dimensions with 1% Sparsity102                            |

| 72. Increase in Throughput for Different Matrix Dimensions with 5% Sparsity102                            |

| 73. Increase in Throughput for Different Matrix Dimensions with 10% Sparsity103                           |

| 74. Throughput Comparison: Sparse Matrix Multiplication Operation105                                      |

| 75. Increase in Throughput for Different Matrix Dimensions with 1% Sparsity106                            |

| 76. Increase in Throughput for Different Matrix Dimensions with 5% Sparsity106                            |

| 77. Increase in Throughput for Different Matrix Dimensions with 10% Sparsity107                           |

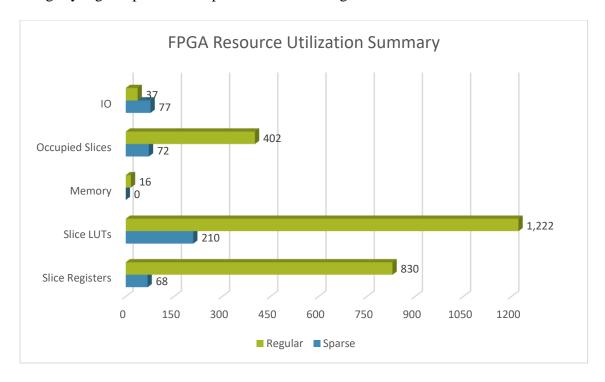

| 78. FPGA Resource Utilization: Regular vs Sparse-Sparse Matrix Multiplication Operation                   |

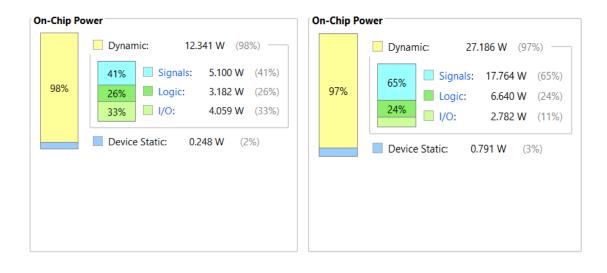

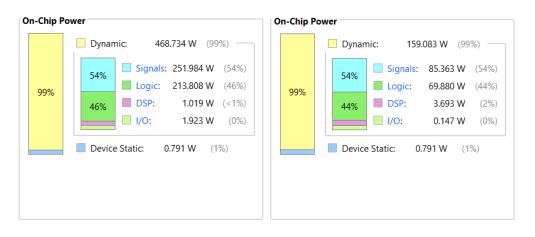

| 79. Power Analysis: Sparse Matrix Multiplication Operation                       | 109 |

|----------------------------------------------------------------------------------|-----|

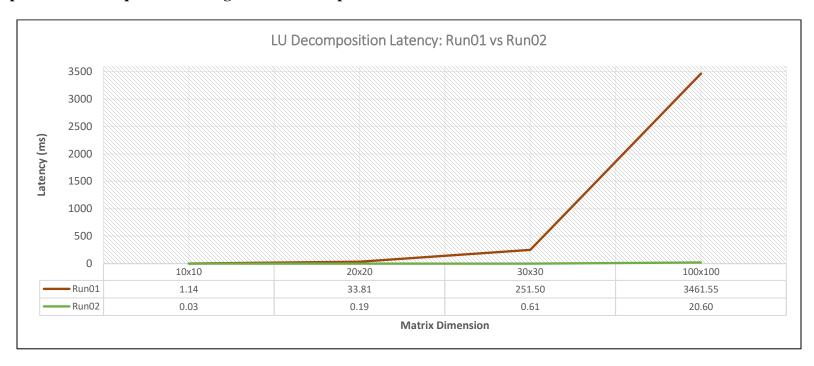

| 80. Latency Comparison: Run01 vs Run02                                           | 110 |

| 81. Throughput Comparison: Run01 vs Run02                                        | 111 |

| 82. FPGA Resource Utilization: Regular vs Sparse-Sparse Matrix LU  Decomposition | 112 |

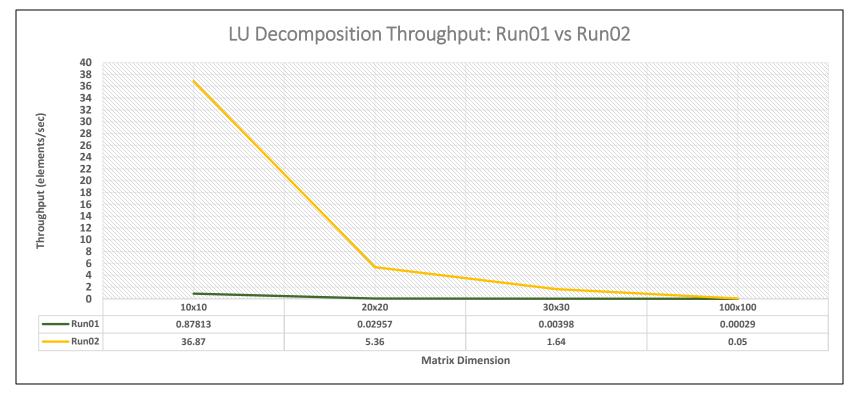

| 83. Power Analysis: Sparse Matrix LU Decomposition                               | 113 |

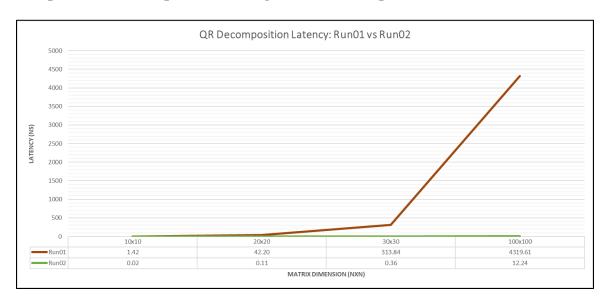

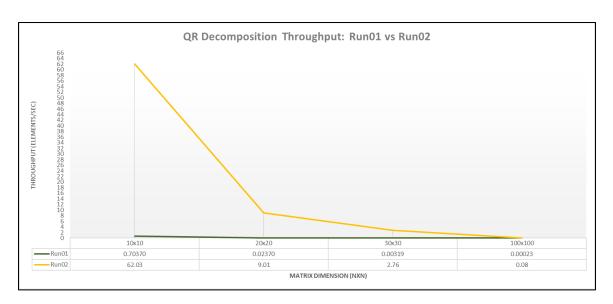

| 84. Latency Comparison: Run01 vs Run02                                           | 114 |

| 85. Throughput Comparison: Run01 vs Run02                                        | 115 |

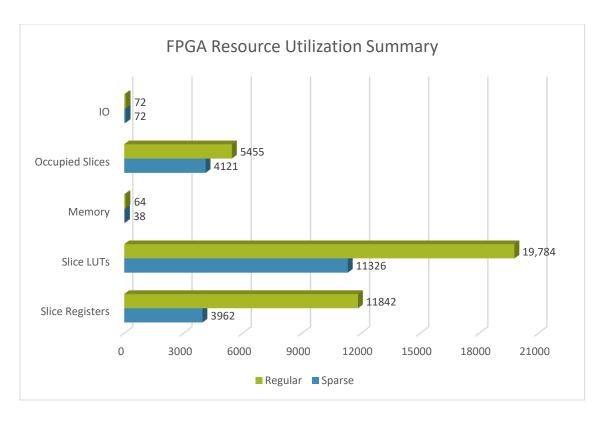

| 86. FPGA Resource Utilization: Regular vs Sparse-Sparse Matrix QR Decomposition  | 116 |

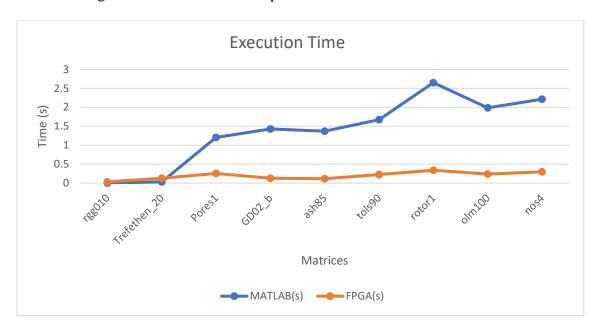

| 87. Comparison of execution time between MATLAB and FPGA                         | 117 |

#### LIST OF ABBREVIATIONS

## **ABBREVIATION**

## **DESCRIPTION**

FPGA Field Programmable Gate Arrays

$N_{lz}$  Length of the largest non-zero diagonal

$N_{dia}$  Number of non-zero diagonal offsets

$N_{mnzr}$  Maximum number of non-zero values

NZV Number of non-zero values in the matrix

r Represents block size

$N_{mnzr}g(i)$  Maximum number of non-zero elements per row

$G_{size}$  Number of rows clumped together to form a group

$N_g$  Number of groups

$N_q$  Number of quadrants

$CSR_{storage}$  Storage space required for CSR

N Order of the matrix

$N_s$  Number of streams

NZS Number of non-zero values per stream

$S_r$  Number of rows per stream

$N_{nzb}$  Number of non-zero blocks in the matrix

$b_{size}$  Block size

$N_{\rm S}$  Number of slices

$N_{nzv}$  Maximum number of nonzero elements

FSM Finite State Machines

MAT\_SIZE Size of the Matrix  $(n\times n)$

ELEMENT\_SIZE Number of Bit (8-bit, 16-bit, 32-bit)

NZE Maximum Number of non-zeros

A\_sr Row of sparse matrix A

*B\_sr* Row of sparse matrix B

A\_sc Column of sparse matrix A

*B\_sc* Column of sparse matrix B

A\_sv Value of sparse matrix A

*B\_sv* Value of sparse matrix B

A\_count Counter to increase index values of matrix A

*B\_count* Counter to increase index values of matrix B

A\_index Index of matrix A

*B\_index* Index of matrix B

#### **ABSTRACT**

The increasing importance of sparse connectivity representing real-world data has been exemplified by the recent work in areas of graph analytics, machine language, and high-performance. Sparse matrices are the critical component in many scientific computing applications, where increasing the sparse matrix operation efficiency can contribute significantly to improve overall system efficiency. The primary challenge is handling the nonzero values efficiently by storing them using specific storage format and performing matrix operations, taking advantage of the sparsity. This thesis proposes an optimized algorithm for performing sparse matrix operations concerning storage and hardware implementation on FPGAs. The proposed thesis work includes simple arithmetic operations to complex decomposition algorithms using Verilog design. Operations of the sparse matrix are tested with testbench matrices of different size, sparsity percentage, and sparsity pattern. The design was able to achieve low latency, high throughput, and minimal resources utilization when compared with the conventional matrix algorithm. Our approach enables solving more significant problems than previously possible, allowing FPGAs to more interesting issues.

#### 1. INTRODUCTION

We live in a "big data" era where Graph Processing has become increasingly important with the amount of data volume generated and collected from many real-world applications such as sensors, social networks, portable devices. As you expect, graphs can sometimes be very complicated. With the demand for data-analysis continuing to grow, large-scale graph processing has become challenging.

A graph consists of a finite set of vertices and a set of edges composed of distinct, unordered pairs of vertices. A dot represents the vertex, and an edge represents a line segment connecting the dots associated with the edge. If one vertex is directed to another vertex by the edges of a graph, then the graph is called directed graph. If it is undirected, then the graph is called undirected graph.

Graph-based applications are used to represent physical structures from social network analyses to anomaly detections. Computing these graphs are entirely determined by specifying either its adjacency structure or its incidence structure. As computers are more adept at manipulating numbers than at recognizing pictures, it is a standard practice to communicate the graph specifications to a computer in matrix form.

Figure 1. Real World Sparse Matrix Applications

Graphs are used to model many systems which are of interest to engineers and scientists today, through which useful information is extracted. Once entered a computer,

the data from real-world applications no longer looks like a graph. Often it is in the form of a sparsely populated matrix with most non-zeros compared to zeros [1]. When the number of zeroes is relatively large, a requirement for more efficient data structures arises. We are drifting away from serial computing towards parallel distributed computing over a large variety of architectural designs. The generic implementation of data structures allows one to reuse the most appealing one, which may not be the fastest.

In a graph algorithm, to obtain information where there is a small number of nonzero entries, but millions of rows and columns of memory could be wasted by storing redundant zeros. There are two ways one would exploit the sparsity of a matrix: One, to save the non-zero elements of a matrix and second is to process only the non-zero elements of a matrix[2]. However, large graphs are hard to deal with as IO limits the state-of-art graph processing systems.

Numerous studies have been addressed to specialize in finding new algorithms for the sparsely distributed matrices. Running parallelized programs on GPU gives large speedup, however high-performance GPUs consume considerable amount of power.

Many computations are difficult to parallelize, incurring extra overhead for transferring data between CPU and GPU. For the most-part, CPUs and GPUs compute well in performance scale. FPGA based designs may avert those problems due to low power nature, with efficient customized pipelines. In a comparison of performance of FPGA and GPU, it is reported both have similar performance, while FPGAs can be 15 times faster and 61 times energy efficient than GPU for uniform random generation [3]. Another work shows GPU implementation can be 11 times faster than FPGA, but on the contrary FPGA implementation can be up to 15 times better than GPU in terms of performance

per watt [4]. It is feasible to get a latency of around or below 1 microsecond using FPGA, whereas with CPU a latency of 50 microsecond is already good. Moreover, one of the main reasons for low latency is they do not depend on generic operating system and the communication do not have to go via generic buses such as USB or PCIe. GPUs multidimensional threading structure or multi core platform is not strongly suitable for highly data-dependent transformations for matrix decomposition. The performance improvement of GPU and multi-core platform-based decomposition algorithms is limited due to the iterative thread sync and irregular memory access [5]. While GPUs shows satisfactory compute efficiency on sparse matrix-matrix operations, they have showed that compute units are significantly underutilized when the sparsity drops below 0.1% achieving low throughput [6]. However, there is a small niche, where FPGA has been an attractive platform which can handle the same computation task for acceleration and achieve high performance with low power computation for many applications. Previous implementation of FPGA based performance improvement for many applications like linear algebra, graphic computation was demonstrated. Compared to other parallel platforms, FPGAs are a better solution for performance improvement by parallelizing decomposition algorithms with flexibility, reconfigurability and low energy consumption.

The primary focus of this work is divided into four subdivisions: Matrix

Operations, Storage Format, software implementation and finally hardware platform.

After carefully reviewing all the previous methods of approaching the sparse matrices,

the next reliable step for improving the performance no longer involves proposing new

expensive optimization but applying the optimizations whenever they are useful.

The primary goal of this project is to develop an efficient algorithm for various sparse matrix operations and compare with the regular matrix operations. By utilizing the sparse matrix storage method, the storage requirements for storing were significantly reduced to be processed in a single FPGA. Finally, the matrix values are sent as input to the FPGA board, performing the necessary matrix operations, and the output values are sent back for verification. The performance calculations are carried out and are represented as individual graphs for comparison.

#### 1.1 Problem Statement

- Indirect addressing: Indirect addresses must address the non-zero entries of a sparse matrix in its index array leading to random accesses that require more memory transactions and lower cache hit rate.

- 2. Memory Allocation: The distribution of zero and non-zero entries are not known in advance. Pre-allocating memory blocks of a specific size may waste memory when the intersection of nodes is large.

- 3. Low Arithmetic Intensity: This is caused by the lack of temporal locality in the access to sparse matrices. If the matrix is not structured or blocked, most of the entries in cache line fetched to get an element remain unused causing high memory overhead per sparse matrix operation.

#### 1.2 Research Goals

To determine an algorithm for various sparse matrix operations by minimizing gate count, area, computational time, latency, number of multiplication & addition hardware and to improve throughput.

- The developed algorithm must be capable of handling matrices of various sizes

and should be simple to implement and highly scalable.

The implementation of the algorithm on an FPGA board involves the following

steps.

- Design of an arithmetic logic unit in Verilog. This unit should implement the Sparse matrix algorithm for arithmetic operations like addition, subtraction, multiplication, as well as decomposition methods including LU and QR decomposition.

- Implement the design of sparse matrix algorithms and optimize for the problem size concerning area, speed, and latency.

- Design of a Universal Asynchronous Receiver/Transmitter (UART)

communication module in Verilog for transferring the data from PC/UART port

for sparse matrix algorithm computation. Results are verified with MATLAB

results for error analysis.

- Comparison of the results and investigate the possible solutions and approaches for scaling up the design for larger matrix more efficiently.

#### 1.3 Goal Measurement Metrics

The two basic hardware design methodologies include language-based design using synthesis tool and schematic-based design. Synthesis tools continue to improve more optimized methods in terms of both area and speed when compared with schematic implementation. The schematic-based design is no longer feasible for supporting architectural complexity for modern FPGAs. Also, this research focuses on reducing the number of multipliers and adders to provide improvements in performance.

For the computation of two sparse matrix operation, there are a certain number of arithmetic operations regardless of the storage of the matrix which include multiplications and addition of nonzero values. The primary goal of the thesis is to improve efficiency and reduce the resources used for the operation. The performance analysis is calculated in terms of improvements in latency, computation time, throughput for performing matrix operations and which reduces the number of multiplication and additions hardware utilize.

#### Latency

It is the amount of time for completing an operation. This is defined as the time between reading the first element of the input matrices, A and B, and writing the first element to the result matrix C. The Latency of an operation is calculated based on the number of clocks consumed by the Hardware accelerator to produce an output after the application of the input (i.e.) the time from reading the first element of input matrix and writing the first element to output matrix.

$$Total\ Time = T_{out} - T_{in}$$

where  $T_{out}$  – time taken for the last output to be calculated;  $T_{in}$  – time taken for the first input to become available

Total Number of Clock Cycles

$$(T_c) = \frac{Total Time}{Clock\_Period}$$

Clock\_Period - timing constraint

Time for one matrix output

$$(T_m) = T_c \times T_{min}$$

where  $T_{min}$  – Minimum period of the clock for the design during synthesis;

Time for n matrix output

$$(T_n) = T_m \times n \times n$$

where  $n \times n$  – matrix size, with n=10,20,30,...100

# • Throughput

Throughput represents the rate at which the design can process inputs. It is the number of operations executed or produced per unit of time. Through this thesis, 1sec (1000ms) is considered as the unit of time, thus representing the throughput as elements/sec. As latency is defined by the time consumed by the design to produce one element, the throughput over a time interval of one sec can be derived as follow:

$$Throughput(elements/sec) = \frac{1 \, sec}{T_n}$$

where  $n \times n - matrix$  size, with  $n = 10, 20, 30, \dots 100$ .

## • Resource Utilization

The amount of resource available on the FPGA board such as Lookup Tables, Memory, logic registers, BRAM, flipflops, nets and logic interconnects are valuable. A comparison of resources utilized for the proposed method and the regular method is presented for analysis.

# • Power Analysis

The power utilization report provides the static and dynamic power consumption of the implemented design, for which the comparison is provided for data analytics.

#### 1.4 Tools Used

The following tools will be used to carry out synthesis, implementation, and verification of results:

- 1. Digilent Nexys4 DDR FPGA.

- 2. Xilinx ISE Design Tool.

- 3. Vivado Design Suite.

- 4. MATLAB Software

#### 2. LITERATURE REVIEW

The Basic Linear Algebra Subprograms (BLAS) has been used in a wide range of software, which provides basic building block routines for vector and matrix operations [7]. Some of the optimizations for BLAS library on general-purpose processors includes loop unrolling and register blocking. Because many of the optimizations are specific to a platform, ATLAS was implemented which automatically optimizes the numerical software for processors with pipelined designs. Linear Algebra Library (LAPACK) solves system of linear equations, least-square solutions, eigenvalue problems and singular value problems.

The main reason why FPGAs are considered over traditional computer is they can be configured as required by the application. The FPGAs can be reprogrammed to given hardware acceleration which offers the best of both hardware and software. And most importantly they are becoming extremely inexpensive when compared with supercomputers like such as CRAY with millions on logic gates and LUT.

There have been several works done for the acceleration of sparse matrix operations that uses Multicore processor, GPU and FPGA based approaches. The implementation using CPU keeps all the data associated with the operation in cache, while the GPUs largely focus on the efficient memory bandwidth usage, whereas FPGA focus on compressed storage of matrix data to reduce the memory bandwidth requirements. Recently, FPGA implementation have been greatly used in data centers like in, researchers from Microsoft uses an FPGA-based design for accelerating the "Bing" search engine [8].

Most of the studies target Sparse Matrix by Vector Multiplication (SpMV), yet Sparse Matrix by Matrix multiplication (SpMM) has been rarely addressed in prior research. A detailed literature by explains the optimization techniques in sparse matrix multiplication. In [9] Zhuo had proposed an FPGA based design, which demonstrated significant performance improvement over general-purpose processor for matrices with irregular sparsity structures. There was another implementation for FPGA based SpMM using a single FPGA node showing how sparsity of a single matrix is affecting the performance of the operations [10]. In [11] the authors have proposed separate architecture for matrix multiplication, where operation speed is a main issue. The pipelining and parallel processing of elements were used to decrease the computation time in [12]. The former method has considered area and latency, while the second had taken area and maximum running frequency considering the energy dissipation.

Some of the works on efficient sparse LU Decomposition architecture for sparse matrices are either Target Domain-Specific pattern targeting a specific application domain or require pre-ordered symmetric matrix. Only a few FPGA-based architectural designs for Sparse LU Decomposition have been proposed due to:

- a. These sparse matrices have irregular sparsity structure, and it is difficult to devise an efficient and common hardware design for all application domains.

- b. A detailed study on the nonzero structure of the sparse matrix is to be performed for designing suitable input parameters for the hardware design.

Consider the work by [13], where author proposes an efficient LU Decomposition hardware Architecture targeting the Power Flow Analysis Application Domain implementing right-looking algorithm along with mechanisms for pivoting operations.

But the performance of the work is primarily I/O bandwidth limited. Whereas in [14], the work is primarily dependent for Circuit Simulation Application domain. The author proposed in a matrix factorization graph which is generated to capture the static sparsity pattern of the matrices and is exploited for distributing the explicit data flow representation of computation across PE's. In the work on [15], a more general hardware design for sparse LU Decomposition was proposed for a wider range of application domains. The hardware architecture parallelizes Left-looking Algorithm to efficiently decompose position symmetric positive definite or diagonally dominant matrices. This design is indeed efficient except for the fact, when the performance of the design arises from dynamic data dependency during column-by-column factorization leading their processing elements stalling for synchronizing to resolve data dependency. Also, the matrices used as benchmarks are either semi-dense or symmetric in topology but none in terms of nonzero elements. The hardware utilization of some of the previous implementations on reconfigurable architectures including Multicores, GPU and FPGA never exceeded 20% mark. The main reason for this poor performance is the irregularity of computation and memory access. The hardware resource utilization of sparse algorithm is very high, because of large hardware dynamic scheduling which is limited by scalability.

The previous FPGA implementations adopts dynamic dataflow, incurring in large overhead and poor hardware resource utilization. The proposed algorithm in this thesis introduces a synchronous dataflow FPGA implementation addressing the main problems of Sparse Operations. A customized data storage format is employed to organize memory access to eliminate time-consuming data address calculations. One of the limiting factors

is the time required for pivot search. Reducing the pivot search during LU decomposition of eliminating will lead to higher performance gain. In our work, we had improvement by overlapping the next pivot search with the current update unit, which although depends on reuse of rows from an elimination step.

The first QR Decomposition was used in weight computation for adaptive beamforming application [16]. In [17] a Squared Givens Rotation algorithm was used to avoid the square root operation. The was followed up by the work of [18] which used SGR algorithm for implementing a linear array on Xilinx Virtex-E FPGA allowing a maximum of 9 processors and achieving 150MHz clock rate and throughput of 20GFLOPS with floating point operation. The first implementation of linear array architecture using CORDIC algorithm for rotation computing was developed. There are many commercial QR-D IP cores using CORDIC algorithm. An algorithm for Inverse QR-based decomposition was proposed by S. Thomas Alexander and Avinash L. Ghirnikar [19] which was later applied to adaptive beam forming. A fixed-point QR decomposition was developed with modified Gram-Schmidt (MGS) algorithm using LUT based approach. Later for polynomial matrices, Polynomial Givens rotation [20] was developed.

#### 3. BACKGROUND

# 3.1. Graph Processing

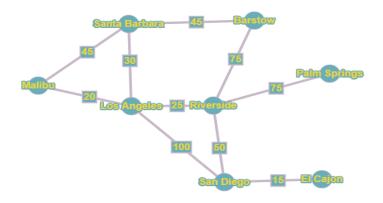

Graphs are a collection of nodes and edges. The edge of the graph provides a connection between one node to another. By default, an edge is bidirectional. Typically, graphs are used to model collection of things along with their relationships. For example, Figure 2 shows a graph with cities as nodes and roads connecting them as edges. The graph represents several cities in Southern California. Vertices represent the cities in the graph while the fact that an edge connecting two vertices show two of the cities connected.

Figure 2. Graph Representing Several Cities in Southern California

Since the structure of real-world graphs can vary tremendously, there is a need for an efficient algorithm for obtaining high performance [21]. When these graphs are processed in a computer, they get stored in the form of an adjacency matrix. For a graph with n nodes, an adjacency matrix is represented as an n×n two-dimensional array. For a weighted graph, the array elements would give the cost of the edge between them, and for an unweighted graph, the array would be Booleans. The following Table 1 is an example of an adjacency matrix representation of the graph in the table. The able in Figure 1

shows the graph is represented as a sparsely populated matrix. The number of rows and columns is equal to the number of vertices in the graph. The edge is represented by intersecting rows and columns of two vertices it connects.

Table 1. Adjacency Matrix Representation of the Graph

|               | MALIBU | SANTA<br>BARBARA | LOS<br>Angeles | RIVERSIDE | BARSTOW | PALM<br>SPRINGS | SAN DIEGO | EL CAJON |

|---------------|--------|------------------|----------------|-----------|---------|-----------------|-----------|----------|

| Malibu        | 0      | 45               | 20             | 0         | 0       | 0               | 0         | 0        |

| SANTA BARBARA | 45     | 0                | 30             | 0         | 45      | 0               | 0         | 0        |

| Los Angeles   | 20     | 30               | 0              | 25        | 0       | 0               | 100       | 0        |

| RIVERSIDE     | 0      | 0                | 25             | 0         | 75      | 0               | 0         | 0        |

| BARSTOW       | 0      | 45               | 0              | 75        | 0       | 0               | 0         | 0        |

| PALM SPRINGS  | 0      | 0                | 0              | 75        | 0       | 0               | 0         | 0        |

| SAN DIEGO     | 0      | 0                | 100            | 50        | 0       | 0               | 0         | 15       |

| EL CAJON      | 0      | 0                | 0              | 0         | 0       | 0               | 15        | 0        |

The computers are responsible for locating the essential vertices, and once these graphs continue to grow large, the algorithms come into play. The matrix representation of these type of graphs is commonly large and sparsely populated. From the adjacency matrix in table 1, it is evident that there are 64 cells in which only 18 entries contain the nonzero value. For a graph with N vertices, the adjacency matrix comprises N² cells. The betweenness centrality(BC) algorithms are used to find the shortest path between vertices, which is complicated and outside the scope of this thesis, but still, the performance is dominated by sparse matrix multiply performance[22]. When dealing with tens or even hundreds of thousands of vertices extracted from graphs, adjacency matrix becomes too large to be processed. Since, the number of zeros in the sparse matrix is high, multiplying or adding two nonzero values together is low and consumes hardware[23]. During sparse matrix performance on a processor, the frequency of nonzero calculations with computer's clock cycle is little between the ranges of 0.5% to 0.1%

which also directly depends on the size of the matrix. For efficient handling of the sparse matrices, various storage formats can be used to store only the nonzero value, thereby reducing the size of the matrix in memory on an embedded system [24]. As embedded digital systems are limited in both their memory size and their computational power, the key is to make the algorithms faster to reduce the requirements.

"I observed that most of the coefficients in our matrices were zero, i.e., the nonzero were 'sparse' in the matrix, and that typically the triangular matrices associated with the forward and back solution provided by Gaussian elimination would remain sparse if pivot elements were chosen with care" - Harry Markowitz.

## **3.2 Sparse Matrices**

Sparse matrices are generally considered to be populated with zeros than nonzero. There is no rule defining when a matrix is sparse. According to Gilbert, any matrix, which allows special techniques to take advantage of many zeros, is a sparse matrix. When storing and performing operations on a sparse matrix, it is desirable to modify the standard algorithm to take advantage of the sparsity[25]. By nature, sparse data yields savings in memory usage. Sparse matrix arises from data communication networks, connections in electronic circuits, with constraints in a linear or non-linear programming formulation, in the discretization of ordinary or partial differential equations in simulation models[26]. Many of the sparse matrices are used in science and engineering today with larger dimensional; there is a lot of research carried out only to store and operate on the non-zero elements of a matrix. This is true when working on large volumes of data with less spatial locality which would do not fit into a CPU's chip memory cache especially for sparse matrix computations and convolution [27]. There are different and specific

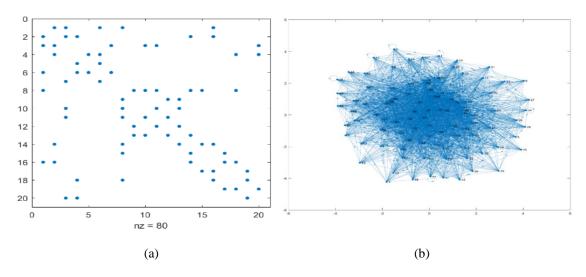

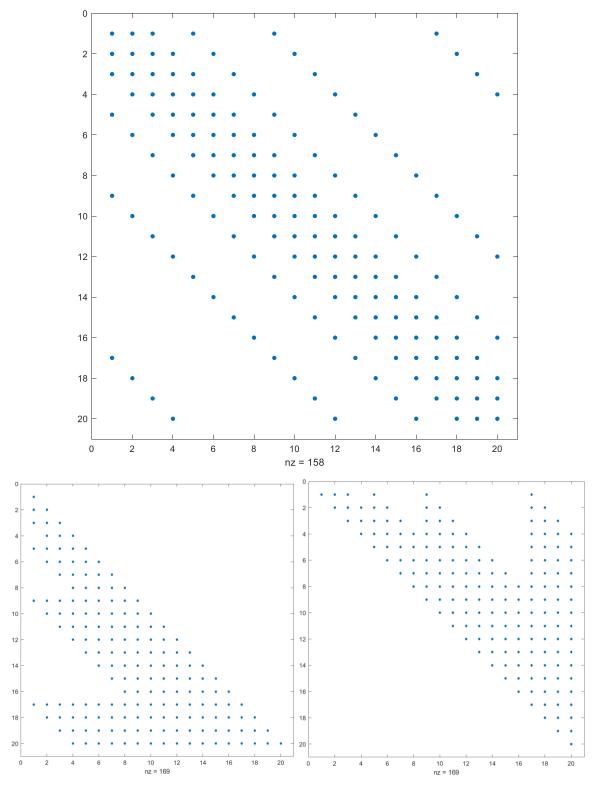

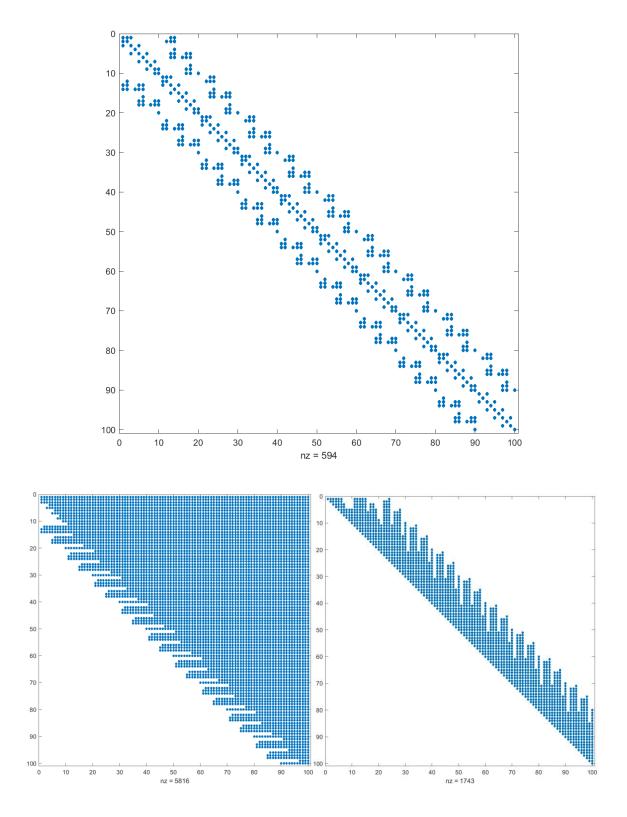

forms of sparsity patterns, where indices are used so that one can know where the nonzero is located within the matrix. To maximize the performance of sparse matrix operations, it is especially important to optimize the operations and not just within individual operations. In Verilog and VHDL, there will always be more than one way to code the same problem. It also provides several alternatives to the designer as to how to accomplish the same task. Therefore, a choice of a coding style is needed to achieve specific performance goals and to minimize resource utilization on a chip. The computational complexity of sparse operations is proportional to the number of nonzero elements in the matrix. The storage of a given sparse matrix will be O(nonzeros). The time required for particular operation on the sparse matrix is close to O(flops). Figure 3(a) is a representation of 20% sparsely populated 20×20 matrix with 80 nonzero values, and Figure 3(b) is a representation of 30% sparsely populated 100×100 matrix with 3000 nonzero values.

Figure 3. Sparsity Pattern of Matrices

Sparse matrices are useful for computing large scale applications that dense matrices cannot handle. The finite element method is one way of solving partial

differential equations where the coefficients are usually sparse. The size of the coefficient is large for getting an accurate approximation to solve PDEs and rely on sparse matrix operations.

## **3.3 Sparse Matrix Storage Formats**

Numerous efforts have been devoted to data storage formats with the aim of maximizing performance. To fully optimize the sparse matrix operations, we will have to design a compression algorithm which will take the sparse matrices structures into account. The section of the thesis briefly describes the most common compression/storage formats to date. The primary goal of these different format variations relies on either improve the architectures ability to access the nonzero data and to perform computations by reducing the total space required to store the matrix[28]. Out of all the formats, Compressed Sparse Row (CSR) is the most common format regardless of the processor which stores the elements row-wise. Another form is the Compressed Sparse Column (CSC) that stores the elements column-wise.

There are many methods for storing only the nonzero elements of a sparse matrix out of which the following have gained a lot of attention due to their computational capability and the efficiency in storing the elements.

- 1. Compressed Row Storage (CRS)

- 2. Compressed Column Storage (CCS)

- 3. Block Compressed Row Storage (BCRS)

- 4. Compressed Diagonal Storage (CDS)

- 5. Coordinate Format (COO)

Table 2 gives a summary of the various storage formats used for implementation, their storage space computation depending on the number of nonzero values available in the sparse matrix, their advantage, and disadvantage.

Table 2. Comparison of Various Sparse Matrix Storage Formats

| Storage<br>Format                       | Storage Space                      | Advantage                                                                     | Disadvantage                                                                                         |  |

|-----------------------------------------|------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

|                                         | <b>Basic Storage Formats</b>       |                                                                               |                                                                                                      |  |

| Coordinate<br>Format<br>(COO)           | $3 \times NZV$                     | It is suitable for<br>any random<br>sparse matrix.                            | It occupies a lot of space.                                                                          |  |

| Compressed<br>Sparse<br>Column<br>(CSC) | $2 \times NZV + n + 1$             | This reduces storage allowing row pointers to facilitate fast multiplication. | Not suitable for GPU due to load imbalance, reduce parallelism and irregular memory access patterns. |  |

| Diagonal<br>Format                      | $N_{dia} + N_{lz} \times N_{dia}$  | It is very effective for matrix with non-zero elements only in the diagonal.  | It is applicable only for matrices whose diagonal elements are non-zeros.                            |  |

| ELLPACK                                 | $2(N_{mnzr}\times m)$              | It is well suited<br>for semi-<br>structured and<br>unstructured<br>meshes.   | It requires to know the maximum number of nonzero elements present in the matrix.                    |  |

| Compressed<br>Sparse Row<br>(CSR)       | parse Row $2 \times NZV + m + 1$   |                                                                               | It uses one-<br>dimensional<br>arrays.                                                               |  |

| Block Based Storage Formats             |                                    |                                                                               |                                                                                                      |  |

| Blocked CSR<br>Format                   | $(N_{nzb}\times 2r)+N_{nzb}+m/r+1$ | It reduces the number of load operations.                                     | It requires an extra loop for matrix operation and suffers from additional overhead.                 |  |

| Row-Grouped<br>CSR Format                              | $2X + m + N_{g}$ $X = \sum_{i=1}^{N_{g}} (N_{mnzr}g(i)) \times G_{size}$                                       | Number of allocated elements per row vary from one group to another group.      | It is time<br>consuming<br>process and<br>requires 4<br>arrays             |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Quad Tree<br>CSR Format                                | $N_q \times \mathit{CSR}_{storage}$                                                                            | Sparse matrix<br>vector<br>multiplication is<br>faster.                         | It requires space overhead                                                 |

| Minimal Quad<br>Tree Format<br>(MQT)                   | $Min(MQT)_{storage}$ $= 4 \times (N/3 + log_4(n^2/N))$ $Max(MQT)_{storage}$ $= 4 \times N(1/3 + log_4(n^2/N))$ | It is efficiently<br>used in I/O<br>operations                                  | It requires space<br>overhead in<br>storing the<br>pointers                |

|                                                        | Vectorizable Format                                                                                            |                                                                                 |                                                                            |

| Compressed<br>Multi-Row<br>Storage<br>Format<br>(CMRS) | $(3 \times NZV) + N_s + 1$                                                                                     | It does not<br>require any zero<br>padding and<br>row and column<br>reordering. | It is suitable only for GPU architecture                                   |

| Adaptive CSR<br>Format                                 | $2 \times NZV + m + 1$                                                                                         | It is effective<br>for GPU<br>specific formats                                  | The transformation overhead poses storage and runtime overhead             |

|                                                        | Streamed Storage Format                                                                                        |                                                                                 |                                                                            |

| Streamed CSR<br>Format                                 | $2(N_s \times \max(NZS)) + S_r + 1$                                                                            | It improves the computation speed                                               | It is suitable for<br>coprocessor<br>SIMD<br>architecture<br>only          |

| Streamed<br>BCSR Format                                | $N_S \times (N_{nzb} \times b_{size}) + 2(N_{nzb})$                                                            | It provides<br>better speedup<br>than BCSR                                      | It is suitable for<br>coprocessor<br>SIMD<br>architecture<br>only          |

| Sliced<br>ELLPACK-C-<br>Sigma Format                   | $N_S + 1 + 4 \times (\sum\nolimits_{i=1}^{N_S} N_{nzv}(i))$                                                    | It reduced the<br>number of zero<br>padding.                                    | Sorting globally<br>will reduce the<br>spatial and<br>temporal<br>locality |

The storage format used to store the nonzero values of the given sparse matrix  $\mathbf{A}$  with size  $\mathbf{N} \times \mathbf{N}$  row-size using three one-dimensional arrays. Let nnz denote the number of nonzero elements of  $\mathbf{A}$ . The first array is called ROW and is of length  $\mathbf{M} + 1$ , i.e., one

entry per row, plus one which contains the row index of **A** where the nonzero element is located. ROW array of the matrix **A** extends from the start of one row to the last row of size **N**×**N**. The last entry of the **ROW** array will be the last row of the matrix depending on the nonzero elements of the matrix. The second array is called **COL**, which contains the column index of matrix **A** where the nonzero element is located. The **COL** array entries start from the first column until the last column, based on the number of columns available. The third array is called **VALUE** and is of the length of the number of nonzero. This array holds the values of all the nonzero elements of matrix **A** investigating left-to-right and then top-to-bottom order. A depiction of the sparse matrix **A** is shown with the storage format used in this thesis in the below figure.

Figure 4(a). Sparse matrix A

$$ROW = [0 \quad 0 \quad 1 \quad 2 \quad 3 \quad 4 \quad 4 \quad 5 \quad 7 \quad 8]$$

$COL = [4 \quad 6 \quad 4 \quad 8 \quad 1 \quad 2 \quad 6 \quad 2 \quad 5 \quad 0]$

$VAL = [1 \quad 3 \quad 2 \quad 1 \quad 3 \quad 3 \quad 1 \quad 3 \quad 6 \quad 0]$

Figure 4(b). Sparse matrix **A** in storage format

Figure 4. Storage of Input Matrix

An analysis of five FPGA-based architectures indicates COO format achieves higher efficiency at the cost of locally storing a copy of vector in each processing element (PE) by eliminating references to the vector.

#### 3.4 Finite State Machines (FSMs)

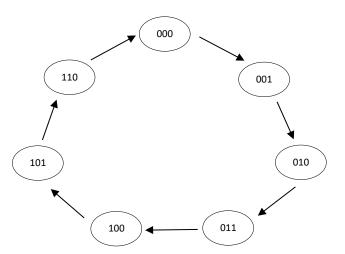

Finite State Machines (FSMs) are a useful abstraction for sequential circuits with "states" of operation. It has a final internal memory, and the operation of FSM begins from one state goes through a transition to different states. Due to their simplicity, they are quick to implement easy for implementation and fast in execution [29]. At each clock edge, combinational logic block computes outputs and next state as a function of inputs and present state. One of the critical factors for optimizing an FSM design is the choice of state coding, which influences the complexity of the logic functions, the hardware costs of the circuits, timing issues, power usage, etc. One of the disadvantages is that it is not suitable for all domain problems, but only when all the state transitions and conditions need to be known upfront and defined. Some of the FSM encoding styles are one-hot, gray code, Johnson code, Compact, Sequential, and Speed1. Each encoding technique has their performance improvements. Speed1 encoding style was able to achieve higher timing performance for matrix operations on an FPGA board. The state transition of speed1 encoding style is shown in Figure 5.

Figure 5. State Diagram of a Simplified Finite State Machine

## 3.5 Field Programmable Gate Arrays (FPGAs)

**3.5.1 FPGA Architecture.** FPGAs are digital integrated circuits (ICs) belonging to a family of Programmable Logic Devices (PLD). The FPGA chip includes I/O blocks and core programming fabric. These I/O blocks are located around the periphery of the chip, which provides programmable I/O connections for various I/O standards. It also consists of Configurable Logic Blocks (CLB) and programmable routing architectures. The appropriate configuration is used in an FPGA for implementing any digital circuit considering the available resources on the board. The figure shows a general FPGA fabric, which represents a popular architecture in the FPGAs, are based. Many different architectures with programming technologies have evolved to provide better results making them the economically viable alternative to Application Specific Intergerat4ed Circuits (ASIC). FPGA's offers excellent flexibility than ASIC's and offers low-level optimization opportunities to improve run-time performance. It has been proved they are considerably more power efficient than multi-core CPUs and GPUs. These logic chips can be reconfigured to implement custom applications. This results in lower time-tomarket than traditional ASIC making them significantly faster than general-purpose hardware. It has the necessary resources such as the Look-Up Tables (LUT), Flip-Flops (**FF**), Digital Signal Processors (**DSP**) and Block Ram (**BRAM**) available in-built for implementing logical functions and arithmetic operations [30].

Modern FPGAs provide superior logic density, low chip cost, and better performance improvements. It can be used to implement systems that need to be operated up to 550 MHz in most of the design the entire operation can be performed on a single FPGA, and do not require custom hardware. The typical frequency of FPGA design is in

low hundreds of MHz, but they have a much finer granularity. Figure 6 shows a rough sketch of the FPGA architecture and the design of a logic block.

Figure 6. Sketch of FPGA Architecture and Design of Simple Logic Block

# 3.5.2 Design and Programming.

Figure 7. Vivado Design Suite

The hardware design is primarily implemented using the EDA Tool Vivado Design Suite/Xilinx ISE Design Tool through programming, simulation, synthesis, implementation through debugging and the results are analyzed. Figure 7 shows an overview of the EDA Design Suite.

## 3.5.2.1 Design Entry.

Figure 8. Vivado Project Manager

Figure 8 shows the window of the Project Manager used to manage the implementation from start to end. This block describes the functionality of the design. The design entry can be done by schematic capture or a state transition diagram or by constructing an HDL based model using Verilog/VHDL. The model is built by writing HDL code using a text editor. Recent synthesis tools like Vivado and Xilinx ISE provide facilities for insertion of language templates for easier coding [31]. This step also allows analyzing the internal form for syntax and semantics for the HDL source.

3.5.2.2 Behavioral Simulation. The HDL module designed during design entry if then simulated at the Register Transfer Level (RTL) to establish functional correctness. This is the primary step involving simulation of the code to determine that it is working as per the design and that it will produce the required results. Simulation is essential to get as many bugs out from the HDL module[8]. If an error arises, the design entry step is investigated, and necessary changes are made for a successful simulation.

Figure 9. Vivado Simulation Environment

# 3.5.2.3 RTL Analysis.

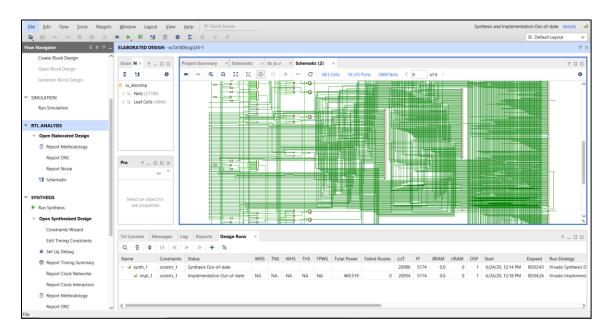

Figure 10. Vivado RTL Analysis Tool

Figure 10 provides how an RTL analysis tool on Vivado Design Suite would be helpful in overseeing the schematic for potential issues. The RTL Analysis is used for analyzing the syntactic and semantic issues, identifying potential implementation issues

with latches and nets. This tool helps in realizing the mapping of LUT onto the FPGA resources.

# 3.5.2.4 Synthesis.

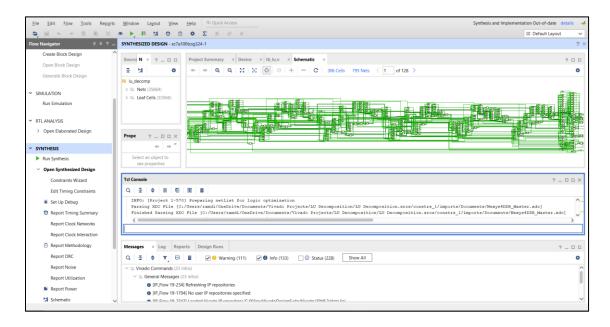

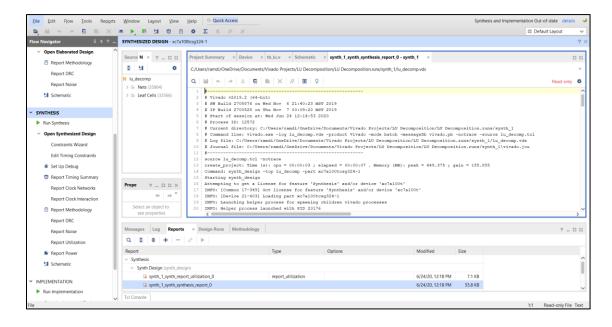

Figure 11. Vivado Synthesis Analysis Tool

Figure 12. Vivado Synthesis Report Analysis

Figure 11 depicts the Synthesis Analysis Tool in managing the nets and logics of the design. The process where the RTL design is translated to gate-level design is called synthesis. Later the design can be mapped to the logic blocks in the FPGA which checks whether the design will meet the timing and area constraints. A device netlist format is created during this step. Figure 12 shows the Report Analysis where the usage of the adders and multipliers are mentioned, for a detailed analysis.

# 3.5.2.5 Implementation.

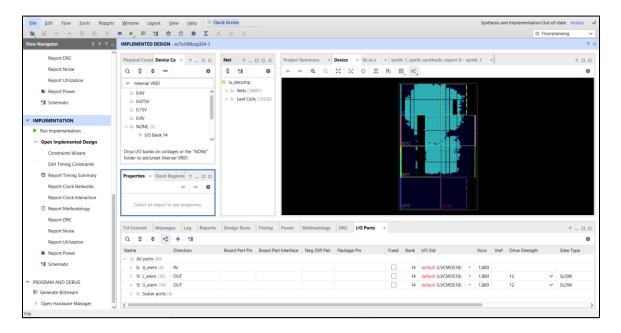

Figure 13. Vivado Implementation Tool

The implementation step consists of the steps of mapping, placing, routing, and generating a BIT file for the HDL design.

#### Mapping

After creating the gate-level netlist, the design is mapped onto the FPGA. The primitives such as function generators, latches or flip-flops used in the target chip are accumulated during this process.

#### • Place and Route

After mapping the design, the primitives are assigned to the Configurable Logic Blocks (**CLB**) during Place and Route step. The primitives are then connected by routing the connections through the switch matrix. The process provides accurate information about the timing delays between parts of the circuit. The design verification process is simulated which is more accurate than the functional simulation.

#### • Bitstream Generation

A bitstream file is created from the physical place and route information.

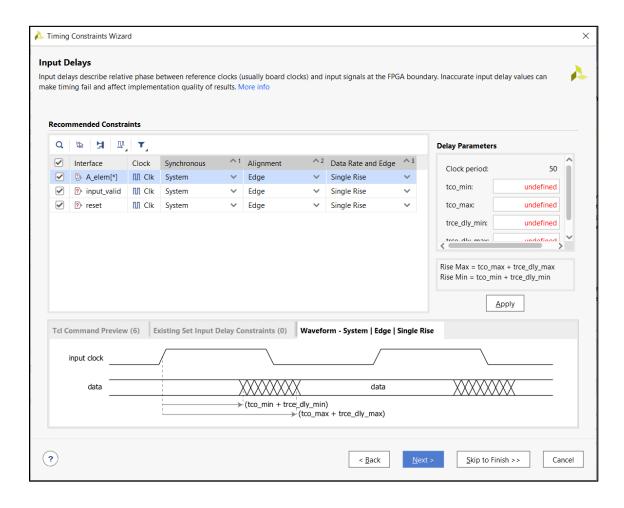

#### 3.5.2.6 Timing Analysis.

Figure 14. Vivado Timing Constraints Tool

Figure 14 is the Timing Constraints Wizard which is used for employing our used desired timing, and analysis. Once the design is mapped, placed, and routed, the delays of the signals and the components of the design are used to produce a new, more detailed netlist leading to a timing accurate simulation.

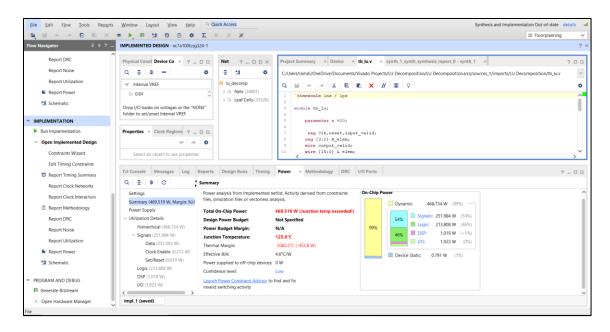

## 3.5.2.7 Power Usage Analysis.

Figure 15. Vivado Power Analysis Tool

Once the timing and area constraints are met with the design implementation, the Power Analysis tool gives the cost of the design in terms of dynamic and static usage of the design.

This tool also provides improvements on the implementation flow to meet the constraints. It automatically identifies the target FPGA board presented and analysis if the design meets the power constraints.

3.5.2.8 Programming the Board. The bitstream file generated is loaded onto the target FPGA. Once the programming of the board is finished, the chip will now be configured to implement the design. The EDA tool used for this thesis work is Vivado Design Suite and Xilinx ISE (Integrated Synthesis Environment) 14.2 using Verilog.

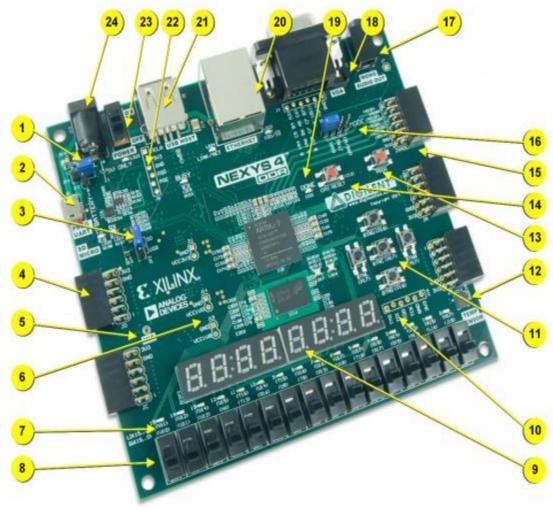

3.5.3 NEXYS4 DDR ARTIX-7 FPGA Board. The FPGA board used for implementing the final design of this project is Nexys4 DDR Artix-7 development board. The Nexys4 DDR board features Artix-7 family processor from Xilinx with the high-performance logic block, more capacity, higher performance, and more resources. This high-capacity FPGA comes with USB, Ethernet, and other ports so hosting designs from combinational circuits to powerful embedded processors is possible. For this thesis, we used UART terminal to send and receive matrix values to and from computer and FPGA board[8]. The board is programmed through JTAG cable, with an E3 pin as Clock port, D4 as UART Transmitter (UART TX) and C4 as UART Receiver (UART RX). The FPGA board is shown in Figure 16, with all the necessary details of the board. The UART connector is marked as number 2 in Figure 15, which also has TX and RX led lights.

| Callout | Component Description                    | Callout | Component Description                |  |

|---------|------------------------------------------|---------|--------------------------------------|--|

| 1       | Power select jumper and battery header   | 13      | FPGA configuration reset button      |  |

| 2       | Shared UART/ JTAG USB port               | 14      | CPU reset button (for soft cores)    |  |

| 3       | External configuration jumper (SD / USB) | 15      | Analog signal Pmod port (XADC)       |  |

| 4       | Pmod port(s)                             | 16      | Programming mode jumper              |  |

| 5       | Microphone                               | 17      | Audio connector                      |  |

| 6       | Power supply test point(s)               | 18      | VGA connector                        |  |

| 7       | LEDs (16)                                | 19      | FPGA programming done LED            |  |

| 8       | Slide switches                           | 20      | Ethernet connector                   |  |

| 9       | Eight digit 7-seg display                | 21      | USB host connector                   |  |

| 10      | JTAG port for (optional) external cable  | 22      | PIC24 programming port (factory use) |  |

| 11      | Five pushbuttons                         | 23      | Power switch                         |  |

| 12      | Temperature sensor                       | 24      | Power jack                           |  |

Figure 16. Nexys4 DDR Artix-7 FPGA Board

30

#### 4. HARDWARE DESIGN ARCHITECTURE

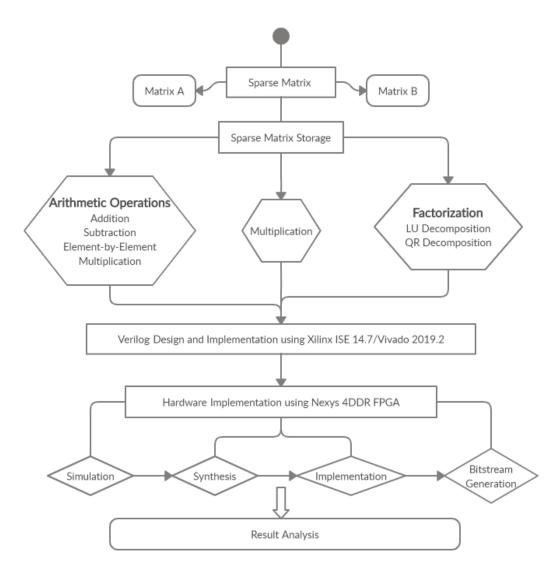

Algorithm for sparse matric arithmetic and decomposition operations are designed, and the operations are implemented in hardware with Nexys4 DDR FPGA Board and the results are compared with conventional matrix operation algorithm. The design approach worked with this thesis is shown in Figure 17. Vivado Design Suite is used for the simulation, synthesis, and implementation of the Verilog design and MATLAB is used for result comparison and error analysis.

Figure 17. High Level Flow Chart of Work Proposed

# • Computational Complexity

Table 3 gives the comparison between the computational complexity of different matrix operations.

Table 3. Computational Complexity

| Matrix Operation     | Input         | Output     | Complexity        |

|----------------------|---------------|------------|-------------------|

| Addition/Subtraction | 2 n×n- matrix | n×n matrix | n <sup>2</sup>    |

| Multiplication       | 2 n×n- matrix | n×n matrix | n <sup>3</sup>    |

| Square root          | 1 n×n- matrix | n×n matrix | n <sup>2</sup> -1 |

| Decomposition        | 1 n×n- matrix | n×n matrix | $1/3 \times n^3$  |

Design and Validation have become a significant step involving various steps from RTL design, logic synthesis, physical design, and verification at an early stage. This makes the testing and verification of a new and complex hardware architecture system a time-consuming process as shown in Figure 18.

Figure 18. FPGA Implementation and Verification Flow

The hardware design for implementation is based on two factors: precision and area.

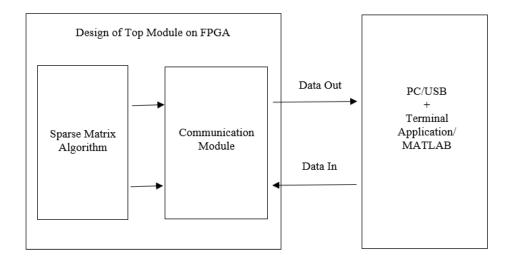

Figure 19. Overview of Hardware and Software Implementation

Figure 19 gives an overview of the module designed and how the communication is established between processor and FPGA for implementation and testing. As illustrated above the objective of this thesis, one of the purposes is to reduce the resources utilized in FPGA [32]. Hence, significant attention was given to the design process implemented, as well as to obtain low latency and high throughput compared to the normal matrix operation [33]. This describes the methodologies than influenced the design and design considerations carried out. The preference of FPGA over traditional CPUs and GPUs is because of the advantages offered by FPGAs and CPLDs. After the matrix algorithm for sparse matrix was studied carefully, the next most significant step was the design itself. The design was done using Verilog because of the ease with which large projects can be managed.

The hardware implementation is split into two major top modules for simplifying the design. The first module is designed to implement the necessary sparse matrix

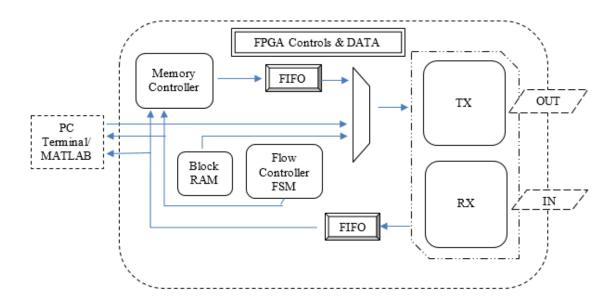

operation like addition, subtraction, multiplication, LU decomposition, QR decomposition algorithms and the necessary computations. And the second module is designed to implement the UART communication and data exchange between the PC to the FPGA hardware board with which it will be communicating. Each of the top modules is subdivided into smaller modules to carry out specific matrix operations with the other modules through internal signals. The Figure 20 gives the flow of how the architecture is designed, along with the flow of memory controllers and transition states.

Figure 20. Block Diagram of TX and RX Module

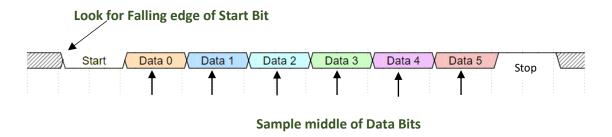

In any asynchronous interface, the first thing we need to know when in time the data should be sampled. If the data is not sampled at the right time, we might get the wrong data. To receive data correctly, the transmitter and receiver must agree on the baud rate. The baud rate if the rate at which the data is transmitted. For example, 9600 baud mean 9600 bits per second.

The Verilog code uses a generic or a parameter to determine how many clock cycles are there in each bit. This is how the baud rate gets determined.

The FPGA is continuously sampling the line. Once it sees the line transition from high to low, it knows the UART data is coming. The first transition indicated the start bit. Once the beginning of the start bit is found, the FPGA waits for one half of a bit period. This ensures that the middle of the data bits gets sampled. From then on, the FPGA just needs to wait once bit period (as specified by the baud rate) and sample the rest of the data. The following Figure 21 is an example of how the output becomes valid when the input clock is high, making the data to be valid for the required operation.

Figure 21. Clock Cycle for TX and RX

This component is used to transfer data over a UART device. It will serialize a byte of data and transmit it over a TXD line. The serialized data has the following characteristics:

- o 9600 Baud Rate

- o 8 bits, LSB first

- o 1 stop bit

- o No parity

- S0\_RDY: This signal goes low once a send operation is begun and remains low until it has completed, and the module is ready to send another bit. The counter that keeps track of the number of clocks cycles the current bit has been held stable over the UART. The combinatorial logic that foes high when the counter has counted to the proper value to the correct baud rate.

- S1\_LOAD\_BIT: The parallel data to be sent. Must be valid the clock cycle when

SEND has gone high. Contains the index of the next bit that needs to be transferred. A register that holds the current data being sent over.

- S2\_SEND\_BIT: Used to trigger a send operation. The upper layer logic should set this signal high for a single clock cycle to trigger a send. When this signal is set high DATA must be valid. Should not be asserted unless READY is high. A register that contains the whole data packet to be sent, including start and stop bits.

Figure 22 captures the FSM diagram of the Transmission bandwidth of the data bit with detailed state transitions and their respective conditions.

Figure 22. Fundamental Design: Transmission FSM

#### RX

The purpose is to double-register the incoming data. This allows it to be used in the UART RX Clock Domain. It removes problems created by metastability.

- S1\_RX\_START\_BIT: Checks the middle of start bit to make sure it is still low. The reset counter resets the middle when the middle value is found.

- S2\_RX\_DATA\_BIT: Waits for CLK\_PER\_BIT-1 clock cycles to sample serial data.

Checks if we have sent out all the bits.

- S3\_RX\_STOP\_BIT: Waits for CLK\_PER\_BIT-1 clock cycles for Stop bit to finish.

- S4\_CLEANUP: Stays for I clock cycle.

Figure 23. Fundamental Design: Receiver FSM

Figure 23 captures the FSM diagram of the Receiver bandwidth of the data bit with detailed state transitions and their respective conditions.

#### 4.1 Arithmetic Operations

- **4.1.1 Sparse Matrix Addition.** The proposed design performs addition operation of two sparse matrices where only the nonzero values are stored, and required operation is performed. The standard matrix addition stores and performs the operation for all the elements inside the matrix regardless of whether the values are zero or not. The design follows the steps below.

- a) A symbolic algorithm, which determined the structure of the resulting matrix.

- A numerical algorithm which determines the values of the nonzero knowing the knowledge of their positions.

$$c_{i,j} = (a_{i,j}) + (b_{i,j})$$

The proposed architectural algorithm performs sparse matrix addition in which the number of rows and number of columns of two matrices should be equal. A parallel implementation of the addition, with enough fast memory algorithm, is proposed.

Consider the matrix addition of **A**+**B**, where **A** has a density **s** percentage with size n×n (square matrix is considered, however, the same methodology can be used for rectangular size), and matrix **B** has a density **s** percentage with size n×n. Density **s** percentage is defined as the number of nonzero elements to the total number of elements in the matrix  $\mathbf{n}^2$ . The matrix addition performs the operation row-wise and column-wise throughout the matrix only for the nonzero elements present leaving behind the zeros. An algorithm for the sparse matrix addition  $\mathbf{A}+\mathbf{B}$  is presented in Listing 1. When addition operation must be performed on both the input matrices, first the number of rows and columns are checked if its equal, i.e., both the matrix should be of the same size. Addition operation

cannot be performed if the matrices are of different size. Then the elements of the matrix are checked row-wise and column-wise from top-to-bottom order for non-zero elements as shown in the figure. Two separate counters  $A\_count$  and  $B\_count$  is used to increment the row and column for both A and B input matrix. This keeps incrementing from A0 to A1 for the size of the matrix. The below Listing 1 shows the pseudo code algorithm for the respective arithmetic operation carries out.

```

Input: A, B

Output: C

Input parameter: MAT_SIZE, ELEMENT_SIZE, NZE

for i \rightarrow 0 to MAT SIZE do

if (A[i] \neq 0) then

Indexing row and column = i + 1

A_sv[i] = A[i]

A_index = A_count + 1

end

if (B[i] \neq 0) then

Index2rc = i + 1

B_index = B_count + 1

B_sv[i] = B[i]

end

if((A\_sr[A\_index] == B\_sr[B\_index]) \&\& (A\_sc[A\_index] == B\_sc[B\_index])) do

Row \le A_sr[A_index]

Col \le A \ sc [A \ index]

Sum \le A_{sv}[A_{index}] + B_{sv}[B_{index}]

end

if (A \text{ sv } [A \text{ index}] \neq 0) then

Row \le A\_sr[A\_index]

Col \le A\_sc[A\_index]

Sum \le A_sv[A_index]

end

if (B \ sv \ [B \ index] \neq 0) then

Row \le B \ sr[B \ index]

Col \le B \ sc[B \ index]

Sum \le B_sv[B_index]

end

end

```

Listing 1. Sparse Matrix Addition Algorithm

The nonzero elements are located from matrix **A**, and the values are stored in the memory  $Mram\_A\_sv$  for the corresponding row and column index  $Mram\_A\_sv$  and  $Mram\_A\_sv$  respectively. Similarly, for the second matrix **B**, the nonzero value gets stored in memory  $Mram\_B\_sv$  for the corresponding row and column index  $Mram\_B\_sv$  and  $Mram\_B\_sv$  respectively. This operation is carried out for the given size of the matrix and is shown in Figure 24 in detail. Once the nonzero is located, the values are stored in terms of row, col, and the corresponding value for which addition operation is to be performed.

Figure 24. Representation of Row and Column Access of Input Matrices

The most important part of this algorithm is the index comparison which is represented as  $A\_index$  for matrix A and  $B\_index$  for matrix B. Initially, once the values are stored the row value of matrix A are compared with the row value of matrix B. If the index of  $A\_sr$  is equal to the index of  $B\_sr$  then the next step of comparing the column value of both the matrices. And, if the index of  $A\_sc$  is equal to the index of  $B\_sc$ , then matrix addition is performed. The  $A\_sc$  is equal to the respective row and

column, i.e.,  $\mathbf{A}_{-}\mathbf{s}\mathbf{v}$  and  $\mathbf{B}_{-}\mathbf{s}\mathbf{v}$  are added with each other as the sum. The assumption is made that the nonzero is located anywhere in the matrix and is highly sparse. Finally, if the nonzero of the same row and same column of matrix  $\mathbf{A}$  does not match with the row and column of matrix  $\mathbf{B}$  directly the value is sent to the output matrix.